International Journal of Intelligent Engineering & Systems

http://www.inass.org/

# Analysis of a High Step-Down DC/DC Converter Topology with a Single Inductor

Kei Eguchi<sup>1\*</sup> Wanglok Do<sup>1</sup> Akira Shibata<sup>1</sup>

<sup>1</sup>Department of Information Electronics, Fukuoka Institute of Technology, Japan \* Corresponding author's Email: eguti@fit.ac.jp

**Abstract:** This paper presents a novel high step-down dc/dc converter topology with a single inductor for 48V data center applications. Distinguished from conventional dc/dc converter topologies with a single inductor, the proposed converter topology is designed by series connecting a step-down cross-connected Fibonacci converter with a buck converter. By combination of these converter modules, the proposed converter topology offers a high voltage gain, viz. 1/48×, without cascade connection. Hence, high power efficiency is provided by the proposed single inductor topology. The characteristics of the proposed converter topology are investigated by theoretical analysis, computer simulations, and experiments. In the given theoretical analysis and the performed simulations, the proposed converter topology demonstrates higher power efficiency than the conventional converter topologies with a single inductor. Furthermore, the validity of the proposed topology is confirmed by the experiments.

**Keywords:** Switched capacitor circuits, Step-down converters, Fibonacci converters, DC/DC converters, High voltage gains, Single inductor converters.

#### 1. Introduction

Recently, due to the shift to cloud computing, electricity power consumption of data centers increases rapidly. For this reason, adopting 48V for data center architecture [1, 2] is receiving much researchers' attention, because the 48V data center architecture can reduce electricity power consumption rather than the conventional data center architectures. To realize such an efficient power distribution system using the 48V data center architecture, several kinds of high step-down power converters have been proposed in past studies.

Saadatizadeh et al. designed two transformerless high step-down dc/dc converters [3], Hajiheidari et al. developed a high step-down dc/dc converter using coupled-inductors [4], Cui et al. and Nene et al. proposed a high step-down phase shift full bridge (PSFB) dc/dc converter [5-8], Zambetti et al. suggested a 48/12 V isolated resonant converter [9], Das et al. proposed a dual-phase multi-inductor hybrid (DP-MIH) converter [10], and Ahmed et al. invented a 48/1 V sigma converter [11, 12]. Furthermore, Ahmed et al. also designed 4:1 and 8:1 LLC dc/dc transformer (LLC-DCX) [13]. These high step-down converters can provide a simple circuit configuration and a high-power efficiency. However, due to the necessity of several magnetic components, such as coupled-inductors and transformers, these conventional converters become bulky.

Distinguished from these approaches using some magnetic components, some researchers have undertaken to develop a step-down power converter without magnetic components. For example, Chang proposed a switched-capacitor-voltage-multiplier/divider dc/dc converter [14] by connecting seriesparallel type converter modules. Wang et al. suggested a ladder-type inductor-less step-down converter [15], Abe et al. suggested a switched capacitor (SC) converter with double conversion topology [16] by connecting ladder type converters with flying capacitors. Saponara et al. developed a high step-down converter by cascading three SC converters [17]. Eguchi et al. designed a step-up/step-down k-Fibonacci dc/dc converter [18] by

modifying a Fibonacci converter. Moreover, Eguchi et al. proposed a nesting-type step-up/step-down converter [19, 20]. These inductor-less step-down converters have some advantages, such as a small electromagnetic interference (EMI), small volume, and a light weight. However, there is a serious drawback of poor output regulation in these inductor-less step-down converters.

To realize an efficient step-down converter which has both properties of these techniques, a hybrid converter topology has been proposed in recent years. For example, a merged two-stage power converter [21-23] was designed by Pilawa-Podgurski et al. and Baek et al. In the merged twostage power converter, Pilawa-Podgurski et al. merged a buck converter with a series-parallel type SC converter. The S-hybrid step-down converter [24] was developed by Seo et al. In the S-hybrid step-down converter, onboard loss can be reduced by combining switched-inductor and switchedcapacitor operations. A dual-phase resonant switched-capacitor-buck converter [25] was proposed by Saggini et al. In the Saggini's converter, high power efficiency can be achieved by connecting a dual-phase buck converter with an SC converter with symmetrical topology [26]. However, these introduced hybrid-type step-down converters [21-25] are not suitable for high step-down applications, because the voltage gain of these stepdown converters is small. Following these studies, Jian et al. invented the switched-tank converter and its families [27-30]. In the switched tank converter, LC resonant tanks are used in the Dickson SC converter. By increasing the number of modules, the switched tank converter can offer a high voltage gain. Uno et al. proposed a pulse width modulation (PWM) based SC converter with switchedcapacitor-inductor cell [31]. By combing a laddertype switched capacitor converter and switchedcapacitor-inductor cells, Uno's converter provides a high voltage gain. However, in all converters

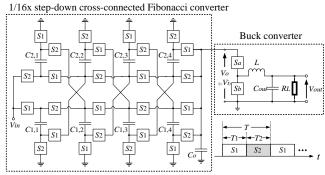

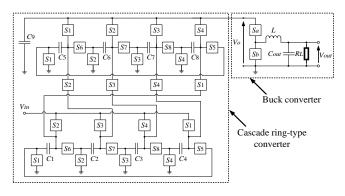

Figure. 1 Topology of the proposed high step-down converter realizing 1/48× step-down conversion

reported in the previous works [27-31], the inductor count also increases in proportion to the number of modules

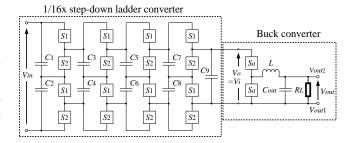

To achieve a high step-down gain with a single inductor, Lazzarin et al. developed a hybrid-type step-down converter by connecting the ladder-type SC converter to the buck converter in series [32]. By cascading ladder converters, the Lazzarin's converter provides a high voltage gain and a flexible output regulation in spite of a single inductor topology. Following this study, Eguchi et al. proposed a single-inductor high step-down converter by connecting cascade ring-type SC converters to a buck converter in series [33]. By using multi-phase control of the cascade ring-type SC converters, the Eguchi's converter can improve power efficiency rather than the Lazzarin's converter [32]. However, due to the cascade connection of SC converter cells. introduced single-inductor step-down converters [32, 33] suffer from a low power efficiency.

In this paper, we propose a novel high step-down dc/dc converter topology with a single inductor for 48V data center applications and analyze its converter topology theoretically. The contributions of this study are the development of a new converter topology and its theoretical evaluation. combining a step-down cross-connected Fibonacci converter and a traditional buck converter, the proposed converter topology offers high steppeddown voltages without the cascade connection of SC converter cells. Concretely, owing to the crossconnected structure, the proposed step-down crossconnected Fibonacci converter achieves the 1/16× step-down conversion without cascade connection. The output of the proposed step-down crossconnected Fibonacci converter is converted again by the buck converter. Hence, in spite of a single inductor topology, the proposed converter can provide not only high voltage gains but also high power efficiency. Of course, owing to the buck converter module, the proposed converter topology with a single inductor enables simple and precise control of the output voltage. To justify the effectiveness of the proposed converter topology, we conduct theoretical analysis, SPICE (Simulation Program with Integrated Circuit Emphasis) simulations, and experiments.

#### 2. Topology of the proposed converter

In this section, we explain the topology of the proposed high step-down dc/dc converter with a single inductor, which is shown in Fig. 1. To achieve a 1/48× voltage gain, the proposed converter

shown in Fig. 1 consists of two converters, namely the 1/16× step-down cross-connected Fibonacci converter and a traditional buck converter. By connecting these converters in series, some remarkable features, viz. a high voltage gain, a single inductor topology, and precise control of an output voltage, are achieved in the proposed converter. In the proposed converter topology, the cross-connected Fibonacci converter realizing step-down conversion is developed based on the step-up cross-connected Fibonacci converter reported in our previous works [34-36]. Unlike the previous converter topologies [34-36], the proposed converter topology shown in Fig. 1 is a step-down dc/dc converter with a single inductor.

The operation principle of the proposed converter topology is as follows. First, the 48V dc input,  $V_{in}$ , is converted by the cross-connected step-down Fibonacci converter. In this converter, the switches  $S_k$  (k = 1, 2) is controlled by two-phase clock pulses. Applying Kirchhoff's voltage law for Fig. 1, the capacitor voltages of  $C_{i,j}$  (For (i = 1, 2) and (j = 1, ..., 4)),  $V_{C_{i,j}}$ , satisfy

$$V_{in} = V_{C_{11}} + V_{C_{22}} + V_{C_{13}} + V_{C_{24}} + V_{C_{14}},$$

(1)

$$V_{in} = V_{C_{2,1}} + V_{C_{1,2}} + V_{C_{2,3}} + V_{C_{1,4}} + V_{C_{2,4}},$$

(2)

$$V_{C_{1,1}} = V_{C_{2,1}} = V_{C_{2,2}} + V_{C_{1,2}}, (3)$$

$$V_{C_{1,2}} = V_{C_{2,2}} = V_{C_{1,3}} + V_{C_{2,3}}, (4)$$

$$V_{C_{1,3}} = V_{C_{2,3}} = V_{C_{1,4}} + V_{C_{2,4}}, (5)$$

and

$$V_o = V_{C_{1,4}} = V_{C_{2,4}}$$

, (6)

where the parasitic elements are neglected. By rearranging Eqs. (1) - (6), the output of the step-down cross-connected Fibonacci converter is expressed as

$$V_o = (1/16) \times V_{in}. (7)$$

The output voltage  $V_o$  of the cross-connected stepdown Fibonacci converter is converted by the traditional buck converter. It is a well-known fact that the voltage gain of the buck converter is D in a continuous mode. Therefore, the proposed converter generates the high stepped-down voltage as follows:

$$V_{out} = DV_o = (D/16) \times V_{in}$$

.  $(0 < D < 1)$  (8)

To help readers' understanding, only the continuous mode is discussed in this paper. By setting D to 1/3, the proposed high step-down converter provides dc

1V from the 48V input. For this reason, the proposed converter topology with a single inductor can offer a high voltage gain and precise control of the output voltage. The detailed analysis of the conventional converters with a single inductor [32, 33] is summarized in Appendices A and B.

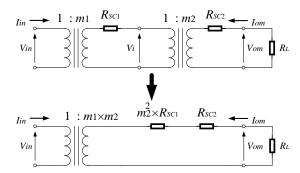

# 3. Theoretical comparison of converter topologies

To clarify the effectiveness of the proposed converter topology, we perform the comparison of converter topologies theoretically, where some theoretical formulas are derived for calculating the maximum power efficiency and output voltage. In the theoretical analysis, the discussion on its control method is omitted to argue the comparison of converter topologies, where the four-terminal equivalent model [37, 38] shown in Fig. 2 is employed to obtain the theoretical formulas. As Fig. 2 shows, the four-terminal equivalent model consists of an ideal transformer and a linear resistor. In this circuit,  $m_1$  is the conversion ratio of the ideal transformer and  $R_{SC1}$  is the internal resistance of the switching converter. In the following, to simplify the theoretical analysis, we obtain the parameters  $m_1$ and  $R_{SC1}$  by assuming the conditions: i) onresistance of all transistor switches  $S_k$  (k=1, 2) is  $R_{on}$ , and ii) time constant is much bigger than the period of clock pulses, T, viz. the variation of electric charges is linear in the capacitors.

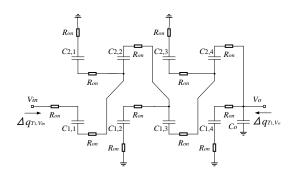

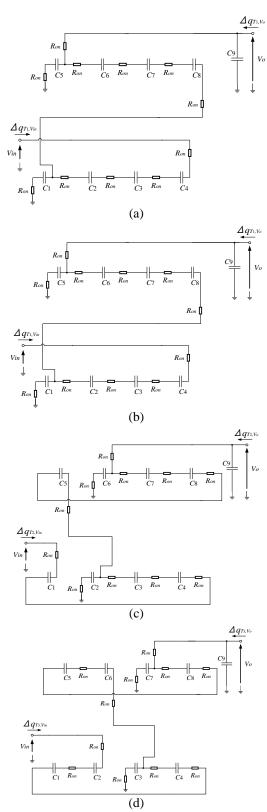

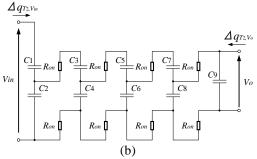

As it can be seen from Fig. 1, the proposed converter can be divided into two blocks: the 1/16× step-down cross-connected Fibonacci converter and the buck converter. First, the equivalent model of the step-down cross-connected Fibonacci converter is analyzed. In a steady state condition, the instantaneous equivalent circuits of the step-down cross-connected Fibonacci converter are expressed as shown in Fig. 3, where  $R_{on}$  is the on-resistance of  $S_k$ ,  $\Delta q_{Tk,vin}$  is the variation of the electric charge in the input terminal, and  $\Delta q_{Tk,vo}$  is the variation of electric charge in the output terminal. In these figures, the sum of the variations in the electric charge of capacitors,  $\Delta q_{Tk}^{i,j}$  (For (i=1, 2) and (j=1, 2)) ..., 4)), is zero in the cycle T. Therefore,  $\Delta q_{Tk}^{i,j}$  in  $C_{i,j}$ satisfies

$$\Delta q_{T_1}^{i,j} + \Delta q_{T_2}^{i,j} = 0, (9)$$

where

$$T = \sum_{k=1}^{2} T_k$$

and  $T_k = T/2$ . (10)

Applying Kirchhoff's current law for Fig. 3, the relationship between the electric charge of  $V_{in}$  in State- $T_k$ ,  $\Delta q_{Tk,vin}$ , and the electric charge of the

Figure. 2 Four-terminal equivalent model

Figure. 3 Instantaneous equivalent circuits of the  $1/16 \times$  step-down cross-connected Fibonacci converter: (a) State- $T_1$  and (b) State- $T_2$

output terminal  $V_o$  in State- $T_k$ ,  $\Delta q_{T_k,v_o}$ , is expressed as follows:

State-T<sub>1</sub>:

$$\Delta q_{T_1, v_{in}} = \Delta q_{T_1}^{1,1}$$

, (11)

$$\Delta q_{T_1, v_o} = \Delta q_{T_1}^{1,4} - \Delta q_{T_1}^{2,4} + \Delta q_{T_1}^o, \tag{12}$$

$$\Delta q_{T_1}^{1,1} = \Delta q_{T_1}^{2,1} + \Delta q_{T_1}^{2,2},\tag{13}$$

$$\Delta q_{T_1}^{2,2} = \Delta q_{T_1}^{1,2} + \Delta q_{T_1}^{1,3},\tag{14}$$

and

$$\Delta q_{T_1}^{1,3} = \Delta q_{T_1}^{2,3} + \Delta q_{T_1}^{2,4}$$

, (15)

State-T<sub>2</sub>:

$$\Delta q_{T_2,v_{in}} = \Delta q_{T_2}^{2,1}$$

, (16)

$$\Delta q_{T_2,\nu_o} = -\Delta q_{T_2}^{1,4} + \Delta q_{T_2}^{2,4} + \Delta q_{T_2}^o, \tag{17}$$

$$\Delta q_{T_2}^{2,1} = \Delta q_{T_2}^{1,1} + \Delta q_{T_2}^{1,2}, \tag{18}$$

$$\Delta q_{T_2}^{1,2} = \Delta q_{T_2}^{2,2} + \Delta q_{T_2}^{2,3},\tag{19}$$

and

$$\Delta q_{T_2}^{2,3} = \Delta q_{T_2}^{1,3} + \Delta q_{T_2}^{1,4}$$

, (20)

In Eqs. (12) and (17),  $\Delta q_{Tk}^{o}$  is the variation of electric charges in  $C_o$ . Furthermore,  $\Delta q_{Tk}^{i,j}$  fulfils

$$\Delta q_{T_1}^{1,j} = \Delta q_{T_2}^{2,j} \text{ and } \Delta q_{T_1}^{2,j} = \Delta q_{T_2}^{1,j},$$

(21)

because the cross-connected Fibonacci converter has a symmetric relationship between Fig. 3 (a) and (b). Using Eqs. (11), (12), (16), and (17), the average input current and output currents,  $I_{in}$  and  $I_{o}$ , are expressed as

$$I_{in} = \frac{\Delta q_{v_{in}}}{T} = \frac{1}{T} \sum_{k=1}^{2} \Delta q_{T_k, v_{in}}$$

(22)

and

$$I_o = \frac{\Delta q_{v_o}}{T} = \frac{1}{T} \sum_{k=1}^{2} \Delta q_{T_k, v_o}$$

. (23)

Insert Eqs. (9)–(21) into Eqs. (22) and (23), we have the relationship between  $I_{in}$  and  $I_{o}$  as

$$I_{in} = -\frac{1}{16}I_o \text{ and } \Delta q_{v_{in}} = -\frac{1}{16}\Delta q_{v_o}.$$

(24)

Therefore, the parameter  $m_1$  is 1/16.

Next, we derive the parameter  $R_{SC1}$  through the discussion on the consumed energy of Fig. 3. In this figure, the total consumed energy  $W_T$  can be expressed as

$$W_T = \sum_{k=1}^2 W_{Tk} = 2W_{T1},\tag{25}$$

because the step-down cross-connected Fibonacci converter has a symmetrical structure. In Eq. (25),  $W_{Tk}$  is the consumed energy of the circuit shown in Fig. 3 in State- $T_k$ , which can be calculated by

$$W_{T1} = \frac{2R_{on}}{T_1} \left( \Delta q_{T_1}^{1,1} \right)^2 + \frac{2R_{on}}{T_1} \left( \Delta q_{T_1}^{2,1} \right)^2 + \frac{2R_{on}}{T_1} \left( \Delta q_{T_1}^{1,2} \right)^2 + \frac{2R_{on}}{T_1} \left( \Delta q_{T_1}^{2,2} \right)^2 + \frac{R_{on}}{T_1} \left( \Delta q_{T_1}^{1,3} \right)^2 + \frac{2R_{on}}{T_1} \left( \Delta q_{T_1}^{2,3} \right)^2 + \frac{2R_{on}}{T_1} \left( \Delta q_{T_1}^{1,4} \right)^2 + \frac{R_{on}}{T_1} \left( \Delta q_{T_1}^{2,4} \right)^2$$

$$(26)$$

Substitute Eq. (26) into Eq. (25), the total consumed energy is rewritten as

$$W_T = R_{on} \frac{\left(\Delta q_{V_o}\right)^2}{T}. (27)$$

On the other hand, the four-terminal equivalent model shown in Fig. 3 has the following total consumed energy:

$$W_T = R_{SC1} \frac{\left(\Delta q_{V_o}\right)^2}{T}.\tag{28}$$

Therefore, from Eqs. (27) and (28), we can easily determine  $R_{SC1}$  as  $R_{on}$ . Finally, by combing  $m_1 = 1/16$  and  $R_{SC1} = R_{on}$ , we can obtain the equivalent model of the step-down cross-connected Fibonacci converter as

$$\begin{bmatrix} V_{in} \\ I_{in} \end{bmatrix} = \begin{bmatrix} 16 & 0 \\ 0 & 1/16 \end{bmatrix} \begin{bmatrix} 1 & R_{on} \\ 0 & 1 \end{bmatrix} \begin{bmatrix} V_o \\ -I_o \end{bmatrix}, \tag{29}$$

because the equivalent circuit of the cross-connected Fibonacci converter can be expressed by Fig. 3.

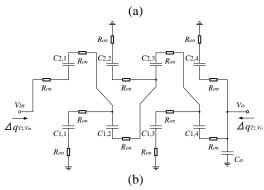

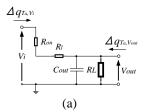

Next, the equivalent model of the buck converter is analyzed under the continuous-mode, where the cycle T is set to

$$T = T_a + T_b$$

,  $T_a = DT$ , and  $T_b = (1 - D)T$ , (30)

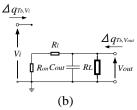

In a steady state condition, the instantaneous equivalent circuits of the buck converter are expressed as shown in Fig. 4, where  $R_{on}$  is the onresistance of  $S_a$  and  $S_b$ ,  $R_l$  is the equivalent series resistance of L,  $\Delta q_{Tj,vi}$  (j=a, b) is the variation of the electric charge in the input terminal of the , and  $\Delta q_{Tj,vout}$  is the variation of electric charge in the output terminal. Applying Kirchhoff's current law for Fig. 4, the relationship between the electric charge of  $V_i$  in State- $T_j$ ,  $\Delta q_{Tj,voi}$ , and the electric charge of the output terminal  $V_{out}$  in State- $T_j$ ,  $\Delta q_{Tj,voi}$ , is expressed as Eqs. (31)–(34), because the buck converter operates in continuous mode.

State-T<sub>a</sub>:

$$\Delta q_{T_a,v_i} = \int_0^{T_a} \Delta i_{T_a}^L(t) dt = \frac{1}{2} DT I_L \cdot (31)$$

and

$$\Delta q_{T_a,v_{out}} = -\int_0^{T_a} \Delta i_{T_a}^L(t) dt + \Delta q_{T_a}^{out}$$

=  $-\frac{1}{2} DT I_L + \Delta q_{T_a}^{out}$ , (32)

State-

$$T_b$$

:  $\Delta q_{T_b, v_i} = 0$  (33)

and

$$\Delta q_{T_b,v_{out}} = -\int_{T_a}^{T} \Delta i_{T_b}^L(t) dt + \Delta q_{T_b}^{out}$$

=  $-\frac{1}{2}(1-D)TI_L + \Delta q_{T_b}^{out}$ . (34)

In Eqs. (31)–(34),  $\Delta i_{T_j}^L(t)$  (j=a, b) is the variation of the inductor currents and  $I_L$  is the amplitude of the

Figure. 4 Instantaneous equivalent circuits of the buck converter used in the proposed converter: (a) State- $T_a$  and (b) State- $T_b$

inductor current. Using Eqs. (30) – (34), the average input and output currents,  $I_i$  and  $I_{out}$ , are expressed as

$$I_{in} = \frac{\Delta q_{v_i}}{T} = \frac{1}{T} \sum_{j=1}^{2} \Delta q_{T_j, v_i}$$

(35)

and

$$I_{out} = \frac{\Delta q_{v_{out}}}{T} = \frac{1}{T} \sum_{j=1}^{2} \Delta q_{T_{j}, v_{out}}.$$

(36)

where  $I_{out}$  corresponds to  $I_o$  in Fig. 2. Insert Eqs. (31)–(34) into Eqs. (35) and (36), we have the relationship between  $I_i$  and  $I_{out}$  as

$$I_i = -DI_{out} \text{ and } \Delta q_{v_i} = -D\Delta q_{v_{out}}.$$

(37)

Therefore, the conversion ratio of the buck converter,  $m_2$ , is D.

In the following, we derive the parameter  $R_{SC2}$  through the discussion on the consumed energy of Fig. 4. In the following theoretical derivation, switching losses are ignored, because the discussion on the control method is omitted to argue the comparison of converter topologies. It is well known that soft switching techniques can reduce switching losses in buck converters. In Fig. 4, the total consumed energy  $W_T$  can be expressed as

$$W_T = W_{T_a} + W_{T_h}. (38)$$

In Eq. (38),  $W_{Tj}$  is the consumed energy of the circuit shown in Fig. 4 in State- $T_j$ , which can be calculated by

$$W_{T_a} = (R_{on} + R_l) \frac{\left(\Delta q_{T_a, v_i}\right)^2}{T_a} \tag{39}$$

and

$$W_{T_b} = (R_{on} + R_l) \frac{\left(\int_{T_a}^{T} \Delta i_{T_b}^{L}(t) dt\right)^2}{T_b}$$

. (40)

Figure. 5 Equivalent model of the proposed high step-down converter realizing 1/48× step-down conversion

Substitute Eqs. (39) and (40) into Eq. (38), the total consumed energy is rewritten as

$$W_T = (R_{on} + R_l) \frac{\left(\Delta q_{V_{out}}\right)^2}{T}.$$

(41)

Therefore, from Eqs. (17) and (41), we can easily determine the internal resistance of the buck converter,  $R_{SC2}$ , as  $R_{on}+R_l$ . By combing  $m_2 = D$  and  $R_{SC2} = R_{on}+R_l$ , we can obtain the equivalent model of the buck converter as

$$\begin{bmatrix} V_i \\ I_i \end{bmatrix} = \begin{bmatrix} \frac{1}{D} & 0 \\ 0 & D \end{bmatrix} \begin{bmatrix} 1 & R_{on} + R_l \\ 0 & 1 \end{bmatrix} \begin{bmatrix} V_{out} \\ -I_{out} \end{bmatrix}. \tag{42}$$

Finally, by combining Eqs. (29) and (42), the equivalent circuit of the proposed converter shown in Fig. 1 can be expressed by

$$\begin{bmatrix} V_{in} \\ I_{in} \end{bmatrix} = \begin{bmatrix} \frac{1}{m_1 m_2} & 0 \\ 0 & m_1 m_2 \end{bmatrix} \begin{bmatrix} 1 & m_2^2 R_{SC1} + R_{SC2} \\ 0 & 1 \end{bmatrix} \begin{bmatrix} V_{out} \\ -I_{out} \end{bmatrix}. (43)$$

because the four-terminal equivalent model of the proposed converter can be illustrated as Fig. 5. From this figure, we get the characteristics as

$$\eta = \frac{R_L}{R_L + m_2^2 R_{Sc1} + R_{Sc2}} \tag{44}$$

and

$$V_{out} = m_1 m_2 V_{in} \times \left(\frac{R_L}{R_L + m_2^2 R_{Sc1} + R_{Sc2}}\right)$$

, (45)

where  $R_L$  is the resistive load. As it can be seen from Eq. (44), the parameters  $R_{SC1}$  and  $R_{SC2}$  have a strong influence on the power efficiency and the output voltage. That is to say,  $R_{SC1}$  and  $R_{SC2}$  are one of the

| Table 1. Characteristics comparison. |                                                                                  |                                      |                                    |

|--------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|------------------------------------|

|                                      | Prop.                                                                            | Conv. [33]                           | Conv. [32]                         |

| $m_1$                                | 1/16                                                                             | 1/16                                 | 1/16                               |

| $m_2$                                | D                                                                                | D                                    | D                                  |

| Gain                                 | D/16                                                                             | <i>D</i> /16                         | <i>D</i> /16                       |

| $R_{sc1}$                            | $R_{on}$                                                                         | $\left(\frac{477}{256}\right)R_{on}$ | $\left(\frac{85}{32}\right)R_{on}$ |

| $R_{sc2}$                            | $R_{on} + R_l$                                                                   | $R_{on} + R_l$                       | $R_{on} + R_l$                     |

| Efficiency                           | $\frac{R_L}{R_L + m_2^2 R_{Sc1} + R_{Sc2}}$                                      |                                      |                                    |

| Output                               | $m_1 m_2 V_{in} \times \left( \frac{R_L}{R_L + m_2^2 R_{Sc1} + R_{Sc2}} \right)$ |                                      |                                    |

most important factors to design of an efficient high step-down converter.

The theoretical performance of the proposed converter topology is compared with that of the existing converter topologies with a single inductor [32, 33]. Table 1 shows the characteristics comparison, where the characteristics conventional converter topologies were analyzed by the same analysis method. Concerning the existing topologies [32, 33], the detailed converter theoretical analysis for deriving the maximum power efficiency and output voltage is explained in Appendices A and B.

As Table 1 shows, the proposed converter topology can achieve the highest power efficiency, because the parameter  $R_{SC1}$  of the proposed converter topology is the smallest. To provide the 1/48× stepped-down voltage, a 1/16× step-down converter is connected to the buck converter in series. Hence, the total performance of the 1/48× step-down converters depends on the performance of the 1/16× step-down converters, namely, crossconnected Fibonacci converter, ladder-type converter [32], and cascade ring-type converter [33]. From Table 1, the proposed converter topology outperforms the conventional converter topologies. In next section, according to the results of the theoretical analysis shown in section 3 and appendices, the converter characteristics in the case of the resistive load are discussed.

### 4. Simulation study

Figure. 6 Simulated results of the 1/16× step-down converters as a function of output power: (a) power efficiency and (b) output voltage

To clarify the effectiveness of the proposed converter, the comparison between the proposed converter and the introduced converters [32, 33] was conducted by using SPICE simulations, where the simulation conditions are as follows:  $V_{in}$ = 48 V,  $R_{on}$ =0.1  $\Omega$ ,  $R_{l}$ =0.45  $\Omega$ ,  $C_{i,j}$  =  $C_{o}$  =33  $\mu$ F,  $C_{out}$ =10  $\mu$ F, L=10  $\mu$ H, and f=1 MHz. In the SPICE simulations, the discussion on its control method is omitted to compare converter topologies.

Fig. 6 is the simulated result of the 1/16× step-down converters as a function of output power. As it can be seen from Fig. 6, the proposed step-down cross-connected Fibonacci converter stands out from the conventional converters in power efficiency and output voltage point of view. Concretely, the proposed converter can achieve about 93% at 6W power efficiency. The proposed converter can improve power efficiency more than 15% at 6W in comparison of the conventional ladder-type converter [32]. Furthermore, the simulation results shown in Fig. 6 are very much consistent with the theoretical results shown in Table 1. From these results, the validity of theoretical analysis can be confirmed.

Fig. 7 demonstrates the simulated results of the  $1/48 \times$  step-down converters with a single inductor. As Fig. 7 shows, the proposed converter outperforms the given converters [32, 33] in power efficiency and output voltage point of view. Concretely, the proposed converter can achieve about 87% at 3W and 76% at 2W in the case of  $D = 1/48 \times 10^{-10}$

Fig. 7. Simulated results of high step-down dc/dc converters with a single inductor as a function of output power: (a) power efficiency and (b) output voltage.

0.7 and D = 0.4, respectively. In other words, the proposed converter can improve power efficiency about 7.5% at 3W and 7% at 2W comparing with the conventional 1/48× step-down converter using a ladder-type converter [32], in the case of D = 0.7and D = 0.4, respectively. However, as it can be seen from the output power shown in Figs. 6 and 7, the output power of the proposed converter is low. Due to the harmful effect in a short circuit fault, the SC converters are difficult to use in high power applications, because there are several capacitors in an SC converter. Of course, we can increase the output power of these high step-down converters by employing the parallel connected topology. In the parallel-connected structure, the users must consider the risk of short circuit faults.

#### 5. Experimental study

In this section, some laboratory experiments were performed concerning the experimental circuit built up with discrete components. The purpose of this experiment study is to confirm the proposed topology, not to characterize it. To perform simple topology confirmation, the experimental circuit was assembled with photo MOS relays AQW 217, Darlington sink drivers TD62083APG, a microcontroller PIC, and electrolytic capacitors. Of course, the switches  $S_1$ ,  $S_2$ ,  $S_a$ , and  $S_b$ , can be realized by power MOSFETs. However, the design of driver circuits is required to use power MOSFETs.

Since the design of peripheral circuits is out of focus of this paper, the photo MOS relays were chosen to assemble the experimental circuit.

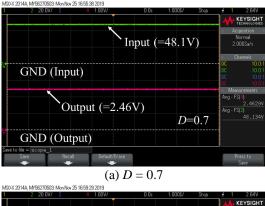

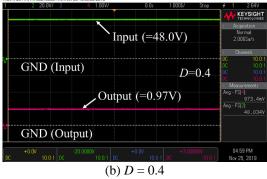

The measured output voltage of the proposed step-down cross-connected Fibonacci converter is demonstrated in Fig. 8. Furthermore, the measured output voltage of the proposed high step-down converter is demonstrated in Fig. 9. The experiments of Figs. 8 and 9 were conducted under the conditions that  $V_{in}$ = 48 V,  $C_{i,j}$  =  $C_o$  =33  $\mu$ F,  $C_{out}$ =100  $\mu$ F, and L=100 mH, and the output load  $R_L$  =100 k $\Omega$ . These experimental conditions also meet the

Figure. 9 Measured output voltage of the high step-down dc/dc converters with a single inductor

assumptions of the theoretical analysis described in section 3. Due to slow switching speed of the photo MOS relays AQW 217, viz. typical turn on time is 0.25 ms and typical turn off time is 0.05 ms, we set the switching frequency f to 40 Hz. This is why the simulation and experiment parameter settings are different. As can be seen from Fig. 8, the measured output voltage is about 2.98 V. In other words, the voltage gain is about 1/16. As it can be seen from Fig. 9, high stepped down voltages were obtained by the experimental circuit. Concretely, the measured output voltage is about 2.46 V and 0.97 V in the case of D = 0.7 and D = 0.4, respectively. In other words, the voltage gain is about 1/19 and 1/53 when D=0.7 and D=0.4, respectively. From these results, we can confirm the validity of the proposed topology through the experiments. However, we

confirmed only the validity of the proposed topology, because the experimental circuit was assembled by using photo MOS relays. Therefore, the detailed investigation through experiments is left to a future study.

#### 6. Conclusion

For 48V data center applications, a novel stepdown dc/dc converter topology consisting of a stepdown cross-connected Fibonacci converter and a traditional buck converter has been proposed in this paper. The performance evaluation of the proposed converter topology was performed by theoretical analysis, SPICE simulations, and experiments.

In the performed theoretical analysis and SPICE simulations, the power efficiency and output voltage of the proposed converter topology are higher than that of the conventional converter topologies, namely the high step-down converter using a laddertype converter and the high step-down converter using a cascade ring-type converter. Concretely, the power efficiency of the proposed converter topology reached about 87% at 3W and 76% at 2W in the case of D = 0.7 and D = 0.4, respectively. In other words, the proposed converter topology improved power efficiency about 7.5% at 3W and 7% at 2W from the conventional converter topology using a ladder-type converter, in the case of D = 0.7 and D =0.4, respectively. Furthermore, the experiments indicated the validity of the proposed topology. In the performed experiment, the high voltage gains, viz.  $1/19 \times$  and  $1/53 \times$ , were obtained in the case of D = 0.7 and D = 0.4, respectively. The proposed hybrid-type high step-down dc/dc converter with a single inductor will contribute to the development of 48V data center applications.

However, this research work lacks experimental confirmation of the obtained theoretical formulas, because the purpose of the experiment shown in Sect. 5 is to confirm the circuit topology, not to characterize it. This is the limitation of this research work. In a future study, we are going to perform the detailed investigation by integrating the proposed converter into an IC chip. The IC implementation of the proposed converter requires the design of peripheral circuits such as driver circuits and controllers. In this paper, we proposed a new converter topology and analyzed it theoretically. The experimental evaluation about power efficiency, power density, etc. requires an integrated implementation in form of an IC chip. Furthermore, the fault analysis of the proposed converter is left to a future study, because the proposed converter

requires several capacitors to achieve high voltage gains.

(2019)thors declare no conflict of interest.

#### **Author Contributions**

Conceptualization, Kei Eguchi; methodology, Kei Eguchi; validation, Akira Shibata and Wanglok Do; formal analysis, Kei Eguchi; investigation, Akira Shibata and Wanglok Do; writing—original draft preparation, Kei Eguchi; writing—review and editing, Kei Eguchi; visualization, Kei Eguchi; supervision, Kei Eguchi;

#### References

- [1] P. Sandri, "Increasing Hyperscale Data Center Efficiency: A Better Way to Manage 54-V/48-V-to-Point-of-Load Direct Conversion", *IEEE Power Electronics Magazine*, Vol. 4, No. 4, pp. 58-64, 2017.

- [2] X. Lyu, Y. Li, Z. Ni, J. Johnson, D. Cao, C. Nan, and S. Jiang, "Composite Modular Power Delivery Architecture for Next-Gen 48V Data Center Applications", In: Proc. 2018 1st Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Xi'an, China, pp. 343-350, 2018.

- [3] C. Pan, C. Chuang and C. Chu, "A Novel Transformerless Interleaved High Step-Down Conversion Ratio DC–DC Converter With Low Switch Voltage Stress", *IEEE Transactions on Industrial Electronics*, Vol. 61, No. 10, pp. 5290-5299, 2014.

- [4] M. Hajiheidari, H. Farzanehfard and E. Adib, "High-Step-Down DC–DC Converter With Continuous Output Current Using Coupled-Inductors", *IEEE Transactions on Power Electronics*, Vol. 34, No. 11, pp. 10936-10944, 2019.

- [5] Y. Cui and L. M. Tolbert, "High step down ratio (400 V to 1 V) phase shift full bridge DC/DC converter for data center power supplies with GaN FETs", In: *Proc. of the 1st IEEE Workshop on Wide Bandgap Power Devices and Applications*, Columbus, OH, pp. 23-27, 2013.

- [6] Y. Cui, W. Zhang, L. M. Tolbert, D. J. Costinett, F. Wang and B. J. Blalock, "Efficiency impact of MOSFET output junction capacitance on a high step down ratio phase shift full bridge DC/DC converter", In: Proc. of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, pp. 2083-2089, 2015.

- [7] H. Nene and T. Zaitsu, "Bi-directional PSFB DC-DC converter with unique PWM control schemes and seamless mode transitions using enhanced digital control", In: *Proc. of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Tampa, FL, pp. 3229-3233, 2017.

- [8] Y. Cui, W. Zhang, L. M. Tolbert, D. J. Costinett, F. Wang and B. J. Blalock, "Two phase interleaved ISOP connected high step down ratio phase shift full bridge DC/DC converter with GaN FETs", In: *Proc. of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Charlotte, NC, pp. 1414-1419, 2015.

- [9] O. Zambetti, M. Colombo, S. D'angelo, S. Saggini and R. Rizzolatti, "48V to 12V isolated resonant converter with digital controller", In: *Proc. of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Tampa, FL, pp. 315-321, 2017.

- [10] R. Das and H. Le, "A Regulated 48V-to-1V/100A 90.9%-Efficient Hybrid Converter for POL Applications in Data Centers and Telecommunication Systems", In: *Proc. of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Anaheim, CA, USA, pp. 1997-2001, 2019.

- [11] M. Ahmed, C. Fei, F. C. Lee and Q. Li, "High-efficiency high-power-density 48/1V sigma converter voltage regulator module", In: *Proc. of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Tampa, FL, pp. 2207-2212, 2017.

- [12] M. H. Ahmed, C. Fei, V. Li, F. C. Lee and Q. Li, "Startup and control of high efficiency 48/1V sigma converter", In: *Proc. of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE)*, Cincinnati, OH, pp. 2010-2016, 2017.

- [13] M. H. Ahmed, F. C. Lee and Q. Li, "LLC Converter with Integrated Magnetics Application for 48V Rack Architecture in Future Data Centers", In: *Proc. of the 2019 IEEE Conference on Power Electronics and Renewable Energy (CPERE)*, Aswan City, Egypt, pp. 437-443, 2019.

- [14] Y. Chang, "Variable-Conversion-Ratio Switched-Capacitor-Voltage-Multiplier/Divider DC-DC Converter", *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 58, No. 8, pp. 1944-1957, 2011.

- [15] W. Wang, J. Kuo and K. Lo, "Development of an Inductorless Step-Down Converter", In: *Proc. of the 2019 10th International*

- Conference on Power Electronics and ECCE Asia (ICPE 2019 ECCE Asia), Busan, Korea (South), pp. 1309-1314, 2019.

- [16] K. Abe, K. Smerpitak, S. Pongswatd, I. Oota and K. Eguchi, "A step-down switched-capacitor AC-DC converter with double conversion topology", *International Journal of Innovative Computing, Information and Control*, Vol. 13, No. 1, pp. 319-330, 2017.

- [17] S. Saponara and G. Ciarpi, "IC Design and Measurement of an Inductorless 48 V DC/DC Converter in Low-Cost CMOS Technology Facing Harsh Environments", *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 65, No. 1, pp. 380-393, 2018.

- [18] K. Eguchi, S. Hirata, M. Shimoji and H. Zhu, "Design of a Step-Up/Step-Down k (=2,3, ...)-Fibonacci DC-DC Converter Designed by Switched-Capacitor Techniques", In: *Proc. of the 2012 Fifth International Conference on Intelligent Networks and Intelligent Systems*, Tianjin, pp. 170-173, 2012.

- [19] K. Eguchi, A. Shibata, T. Ishibashi and I. Oota, "An Inductor-Less Nesting-Type Step-Up/Step-Down AC/AC Converter with a Small Component Count", *International Journal of Innovative Computing*, *Information and Control*, Vol. 15, No. 6, pp. 2377-2384, 2019.

- [20] K. Eguchi, R. Rubpongse, A. Shibata, T. Ishibashi and F. Asadi, "A step-down nesting-type ac–ac converter combined with voltage equalizers and switched-capacitor simple converters", *Energy Reports*, Vol. 6, Suppl. 2, pp. 173-178, 2020.

- [21] R. C. N. Pilawa-Podgurski, D. M. Giuliano and D. J. Perreault, "Merged two-stage power converterarchitecture with softcharging switched-capacitor energy transfer", In: *Proc. of the 2008 IEEE Power Electronics Specialists Conference*, Rhodes, pp. 4008-4015, 2008.

- [22] R. C. N. Pilawa-Podgurski and D. J. Perreault, "Merged Two-Stage Power Converter With Soft Charging Switched-Capacitor Stage in 180 nm CMOS", *IEEE Journal of Solid-State Circuits*, Vol. 47, No. 7, pp. 1557-1567, 2012.

- [23] J. Baek, P. Wang, S. Jiang and M. Chen, "LEGO-PoL: A 93.1% 54V-1.5V 300A Merged-Two-Stage Hybrid Converter with a Linear Extendable Group Operated Point-of-Load (LEGO-PoL) Architecture", In: *Proc. of* the 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), Toronto, ON, Canada, pp. 1-8, 2019.

- [24] G. Seo and H. Le, "S-Hybrid Step-Down DC–DC Converter—Analysis of Operation and Design Considerations", *IEEE Transactions on Industrial Electronics*, Vol. 67, No. 1, pp. 265-275, 2020.

- [25] S. Saggini, S. Jiang, M. Ursino and C. Nan, "A 99% Efficient Dual-Phase Resonant Switched-Capacitor-Buck Converter for 48 V Data Center Bus Conversions", In: *Proc. of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Anaheim, CA, USA, pp. 482-487, 2019.

- [26] K. Eguchi, W. Do, S. Kittipanyangam, K. Abe, I. Oota, "Design of a three-phase switched-capacitor ac-ac converter with symmetrical topology", *International Journal of Innovative Computing, Information and Control*, Vol. 12, No. 5, pp. 1411-1421, 2016.

- [27] S. Jiang, C. Nan, X. Li, C. Chung and M. Yazdani, "Switched tank converters", In: *Proc. of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC)*, San Antonio, TX, pp. 81-90, 2018.

- [28] X. Lyu, Y. Li, D. Cao, S. Jiang and C. Nan, "Comparison of GaN based switched-tank converter and cascaded voltage divider", 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, pp. 158-164, 2017.

- [29] Y. Li, X. Lyu, D. Cao, S. Jiang and C. Nan, "A 98.55% Efficiency Switched-Tank Converter for Data Center Application", *IEEE Transactions on Industry Applications*, Vol. 54, No. 6, pp. 6205-6222, 2018.

- [30] M. Wei, Y. Li, Z. Ni, C. Liu and D. Cao, "Zero Voltage Switching Switched-Tank Modular Converter for Data Center Application", In: *Proc. of the 2019 IEEE 7th Workshop on Wide Bandgap Power Devices and Applications* (WiPDA), Raleigh, NC, USA, pp. 245-250, 2019.

- [31] M. Uno and A. Kukita, "PWM Switched Capacitor Converter With Switched-Capacitor-Inductor Cell for Adjustable High Step-Down Voltage Conversion", *IEEE Transactions on Power Electronics*, Vol. 34, No. 1, pp. 425-437, 2019.

- [32] T. B. Lazzarin, C. Bharatiraja and B. Lehman, "Direct 48V to 1V Step-Down DC-DC Converter", In: *Proc. of the 2018 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES)*, Chennai, India, pp. 1-6, 2018.

- [33] K. Eguchi, A. Shibata and Y. Harada, "A direct high step-down DC/DC converter using

- cascade ring-type converters", *Energy Reports*, Vol. 6, Suppl. 2, pp. 119-124, 2020.

- [34] K. Eguchi, S. Pongwatd, F. Asadi and H. Fujisaki, "A High Voltage Gain SC DC-DC Converter Based on Cross-Connected Fibonacci-Type Converter", In: *Proc. of the 2018 International Conference on Engineering, Applied Sciences, and Technology (ICEAST)*, Phuket, pp. 1-4, 2018.

- [35] K. Eguchi, R. Rubpongse, A. Shibata and T. Ishibashi, "Synthesis and analysis of a cross-connected Fibonacci dc/dc converter with high voltage gain", *Energy Reports*, Vol. 6, Suppl. 2, pp. 130-136, 2020.

- [36] W. Do, H. Bevrani, Q. Shafiee and K. Eguchi, "An analytical approach for design of a cross-connected Fibonacci switched capacitor converter", *Energies*, Vol. 13, No. 2, 431, 2020.

- [37] W. Do, H. Fujisaki, F. Asadi and K. Eguchi, "A Cross-Connected Charge Pump for Energy Harvesting Applications", *International Journal of Innovative Computing, Information and Control*, Vol. 15, No. 3, pp. 969-982, 2019.

- [38] K. Eguchi, Y. Kozono, T. Ishibashi and F. Asadi, "Design of a dual-input cross-connected charge pump utilizing scavenged energy", *Energy Reports*, Vol. 6, Suppl. 2, pp. 228-234, 2020.

### **Appendix**

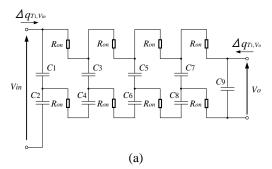

### A.1 Theoretical analysis of the conventional converter using a cascade ring-type converter

In this Appendix, the conventional hybrid-type converter using a cascade ring-type converter shown in Fig. A1 [33] is theoretically analyzed by using the four-terminal equivalent model shown in Fig. 2. In this theoretical analysis, we discuss the theoretical

Figure. A1 Circuit configuration of the conventional hybrid-type 1/48× step-down converter using a cascade ring-type converter

Figure. A2 Instantaneous equivalent circuits of the cascade ring-type converter: (a) State- $T_1$ , (b) State- $T_2$ , (c) State- $T_3$ , and (d) State- $T_4$

analysis of the cascade ring-type converter only, because the characteristics of the buck converter

have already been discussed in Section 3 (Please see Eq. (42)).

In a steady state condition, the instantaneous equivalent circuits of the cascade ring-type converter are shown in Fig. A2, because the cascade ring-type converter is controlled by four-phase clock pulses. In Fig. A2,  $R_{on}$  is the on-resistance of  $S_j$  (j=1, ..., 8),  $\Delta q_{T_i,vin}$  (i=1, ..., 4) is the variation of the electric charge in the input terminal, and  $\Delta q_{T_i,vo}$  is the variation of electric charge in the output terminal.

In Fig. A2, the variation of electric charge,  $\Delta q_{Ti}^{k}$ , in  $C_k$  (k=1, ..., 9) satisfies

$$\sum_{i=1}^{4} \Delta q_{T_i}^k = 0,\tag{A1}$$

because the overall change in  $\Delta q_{Ti}^{k}$  is zero in the cycle *T*. In Eq. (A1), the cycle *T* is set to

$$T = \sum_{i=1}^{4} T_i$$

and  $T_1 = T_2 = T_3 = T_4 = T/4$ . (A2)

In each state of Fig. A2, the variation of electric charge fulfils the followings by using Kirchhoff's current law:

State-T<sub>1</sub>:

$$\Delta q_{T_1, v_{in}} = \Delta q_{T_1}^4$$

, (A3)

$$\Delta q_{T_1,\nu_0} = \Delta q_{T_1}^5 - \Delta q_{T_1}^6 + \Delta q_{T_1}^9, \tag{A4}$$

$$\Delta q_{T_1}^2 = \Delta q_{T_1}^3 = \Delta q_{T_1}^4,\tag{A5}$$

$$\Delta q_{T_1}^6 = \Delta q_{T_1}^7 = \Delta q_{T_1}^8, \tag{A6}$$

and

$$\Delta q_{T_1}^2 = \Delta q_{T_1}^1 + \Delta q_{T_1}^8$$

. (A7)

State-

$$T_2$$

:  $\Delta q_{T_2, v_{in}} = \Delta q_{T_2}^1$ , (A8)

$$\Delta q_{T_2, \nu_0} = \Delta q_{T_2}^6 - \Delta q_{T_2}^7 + \Delta q_{T_2}^9, \tag{A9}$$

$$\Delta q_{T_2}^1 = \Delta q_{T_2}^3 = \Delta q_{T_2}^4,\tag{A10}$$

$$\Delta q_{T_2}^5 = \Delta q_{T_2}^7 = \Delta q_{T_2}^8,\tag{A11}$$

and

$$\Delta q_{T_2}^3 = \Delta q_{T_2}^2 + \Delta q_{T_2}^5$$

. (A12)

State-T<sub>3</sub>:

$$\Delta q_{T_3, v_{in}} = \Delta q_{T_2}^2$$

, (A13)

$$\Delta q_{T_2, \nu_0} = \Delta q_{T_2}^7 - \Delta q_{T_2}^8 + \Delta q_{T_2}^9, \tag{A14}$$

$\Delta q_{T_3}^1 = \Delta q_{T_3}^2 = \Delta q_{T_3}^4,\tag{A15}$

$$\Delta q_{T_3}^5 = \Delta q_{T_3}^6 = \Delta q_{T_3}^8,\tag{A16}$$

Figure. A3 Circuit configuration of the conventional hybrid-type 1/48× step-down converter using a ladder-type converter

Figure. A4 Instantaneous equivalent circuits of the  $1/16 \times$  step-down ladder-type converter: (a) State- $T_1$  and (b) State- $T_2$

and

$$\Delta q_{T_3}^4 = \Delta q_{T_3}^3 + \Delta q_{T_3}^6$$

. (A17)

State-T<sub>4</sub>:

$$\Delta q_{T_4, \nu_{in}} = \Delta q_{T_4}^3$$

, (A18)

$$\Delta q_{T_A, \nu_0} = -\Delta q_{T_A}^5 + \Delta q_{T_A}^8 + \Delta q_{T_A}^9, \tag{A19}$$

$$\Delta q_{T_4}^1 = \Delta q_{T_4}^2 = \Delta q_{T_4}^3, \tag{A20}$$

$$\Delta q_{T_A}^5 = \Delta q_{T_A}^6 = \Delta q_{T_A}^7,\tag{A21}$$

and

$$\Delta q_{T_A}^1 = \Delta q_{T_A}^4 + \Delta q_{T_A}^7$$

. (A22)

Since the average input/output currents,  $I_{in}$  and  $I_{o}$ , can be obtained as

$$I_{in} = \frac{\Delta q_{v_{in}}}{T} = \frac{1}{T} \sum_{i=1}^{4} \Delta q_{T_i, v_{in}}$$

(A23)

and

$$I_o = \frac{\Delta q_{v_o}}{T} = \frac{1}{T} \sum_{i=1}^{4} \Delta q_{T_i, v_o},$$

(A24)

we derive the relationship between  $I_{in}$  and  $I_o$  by substituting Eqs. (A1)-(A22) for Eqs. (A23) and (A24) as follows:

$$I_{in} = -\frac{1}{16}I_o$$

and  $\Delta q_{v_{in}} = -\frac{1}{16}\Delta q_{v_o}$ . (A25)

Therefore, we have the parameter  $m_1$  as 1/16.

Next, in order to obtain  $R_{SC}$ , we analyze the total consumed energy,  $W_T$ , shown in Fig. 2. As it can be seen from Fig. A2, the 1/16 step-down cascade ring-type converter has a symmetrical topology. Therefore, the total consumed energy of the cascade ring-type converter,  $W_T$ , is expressed as

$$\begin{split} W_{T} &= \sum_{i=1}^{4} W_{Ti} = 4W_{T1} \\ &= 4 \times \left\{ R_{on} \frac{\left(\Delta q_{T_{1}}^{1}\right)^{2}}{T_{1}} + 4R_{on} \frac{\left(\Delta q_{T_{1}}^{2}\right)^{2}}{T_{1}} + 4R_{on} \frac{\left(\Delta q_{T_{1}}^{2}\right)^{2}}{T_{1}} + R_{on} \frac{\left(\Delta q_{T_{1}}^{2}\right)^{2}}{T_{1}} + R_{on} \frac{\left(\Delta q_{T_{1}}^{5}\right)^{2}}{T_{1}} + R_{on} \frac{\left(\Delta q_{T_{1}}^{5}\right)^{2}}{T_{1}} + R_{on} \frac{\left(\Delta q_{T_{1}}^{5}\right)^{2}}{T_{1}} \right\} \\ &= \left(\frac{477}{256}\right) R_{on} \frac{\left(\Delta q_{V_{o}}\right)^{2}}{T}. \end{split} \tag{A26}$$

From Eq. (A11), we get  $R_{SC1}$  as  $(477/256)R_{on}$ , because  $W_T$  of Fig. 2 is expressed by Eq. (28). Therefore, the four-terminal equivalent model of the  $1/16 \times$  step-down cascade ring-type converter can be expressed by the K-matrix as follows:

$$\begin{bmatrix}

V_{in} \\

I_{in}

\end{bmatrix} = \\

\begin{bmatrix}

16 & 0 \\

0 & 1/16

\end{bmatrix} \begin{bmatrix}

1 & (477/256)R_{on} \\

0 & 1

\end{bmatrix} \begin{bmatrix}

V_o \\

-I_o

\end{bmatrix}.$$

(A27)

Finally, by combining Eqs. (42) and (A27), we get the characteristics of the conventional hybrid-type  $1/48 \times$  step-down converter shown in Table 1.

# **A.2** Theoretical analysis of the conventional converter using a ladder-type converter

In this Appendix, the conventional hybrid-type converter using a ladder-type converter shown in Fig. A3 [32] is analyze theoretically by using the four-terminal equivalent model shown in Fig. 2. In this theoretical analysis, we also discuss the theoretical analysis of the ladder-type converter only, because the characteristics of the buck converter have already been discussed in Section 3 (Please see Eq. (42)).

Fig. A4 illustrates the instantaneous equivalent circuits of the ladder-type converter are shown in Fig. A4, where  $R_{on}$  is the on-resistance of  $S_i$  (j=1, 2),  $\Delta q_{Ti,vin}$  (i=1, 2) is the variation of the electric charge in the input terminal, and  $\Delta q_{Ti,vo}$  is the variation of electric charge in the output terminal.

Since the overall change in  $\Delta q_{Ti}^{k}$  is zero in the cycle T, the variation of electric charges  $\Delta q_{Ti}^{k}$  in  $C_{k}$  (k=1,...,9) satisfies

$$\Delta q_{T_1}^k + \Delta q_{T_2}^k = 0, \tag{A28}$$

where

$$T = \sum_{i=1}^{2} T_i$$

and  $T_1 = T_2 = T/2$ . (A29)

From Fig. A4, the relationship between the electric charge of  $V_{in}$  in State- $T_i$ ,  $\Delta q_{T_i,vin}$ , and the electric charge of the output terminal  $V_o$  in State- $T_i$ ,  $\Delta q_{T_i,vo}$ , is obtained as

State-T<sub>1</sub>:

$$\Delta q_{T_1,\nu_{in}} = \Delta q_{T_1}^2$$

, (A30)

$$\Delta q_{T_1,\nu_o} = \Delta q_{T_1}^7 - \Delta q_{T_1}^8 + \Delta q_{T_1}^9, \tag{A31}$$

$$\Delta q_{T_1}^4 = \Delta q_{T_1}^2 - \Delta q_{T_1}^4,\tag{A32}$$

$$\Delta q_{T_1}^3 = \Delta q_{T_1}^4 - \Delta q_{T_1}^6, \tag{A33}$$

and

$$\Delta q_{T_1}^5 = \Delta q_{T_1}^6 - \Delta q_{T_1}^8$$

, (A34)

State-T<sub>2</sub>:

$$\Delta q_{T_2, v_{in}} = \Delta q_{T_2}^1$$

, (A35)

$$\Delta q_{T_2,\nu_o} = -\Delta q_{T_2}^7 + \Delta q_{T_2}^8 + \Delta q_{T_2}^9, \tag{A36} \label{eq:A36}$$

$$\Delta q_{T_2}^1 = \Delta q_{T_2}^2 + \Delta q_{T_2}^3,\tag{A37}$$

$$\Delta q_{T_2}^3 = \Delta q_{T_2}^4 + \Delta q_{T_2}^5, \tag{A38}$$

and

$$\Delta q_{T_2}^5 = \Delta q_{T_2}^6 + \Delta q_{T_2}^7$$

. (A39)

Since the average input/output currents,  $I_{in}$  and  $I_{o}$ , can be expressed by

$$I_{in} = \frac{\Delta q_{v_{in}}}{T} = \frac{1}{T} \sum_{i=1}^{2} \Delta q_{T_{i}, v_{in}}$$

(A40)

and

$$I_o = \frac{\Delta q_{v_o}}{T} = \frac{1}{T} \sum_{i=1}^{2} \Delta q_{T_i, v_o},$$

(A41)

Substituting Eqs. (A28)–(A39) into Eqs. (A40) and (A41), the relationship between  $I_{in}$  and  $I_o$  can be obtained as

$$I_{in} = -\frac{1}{16}I_o$$

and  $\Delta q_{v_{in}} = -\frac{1}{16}\Delta q_{v_o}$ . (A42)

DOI: 10.22266/ijies2021.0228.51

International Journal of Intelligent Engineering and Systems, Vol.14, No.1, 2021

Therefore, we get the parameter  $m_1$  as 1/16.

Next, in order to obtain  $R_{SC}$ , we analyze the total consumed energy,  $W_T$ , shown in Fig. 2. Since energy is consumed by  $R_{on}$ , the total consumed energy of the cascade ring-type converter,  $W_T$ , is expressed as

$$W_T = W_{T1} + W_{T2}, \tag{A43}$$

where  $W_{T1}$  and  $W_{T2}$  can be calculated by

$$\begin{split} W_{T1} &= R_{on} \frac{\left(\Delta q_{T_1}^2 - \Delta q_{T_1}^4\right)^2}{T_1} + \\ R_{on} \frac{\left(\Delta q_{T_1}^2 - \Delta q_{T_1}^4 - \Delta q_{T_1}^3\right)^2}{T_1} \\ &+ R_{on} \frac{\left(\Delta q_{T_1}^2 - \Delta q_{T_1}^4 - \Delta q_{T_1}^3 - \Delta q_{T_1}^5\right)^2}{T_1} + \\ R_{on} \frac{\left(\Delta q_{T_1}^4 - \Delta q_{T_1}^4\right)^2}{T_1} \\ &+ R_{on} \frac{\left(\Delta q_{T_1}^2 - \Delta q_{T_1}^4\right)^2}{T_1} + \\ R_{on} \frac{\left(\Delta q_{T_1}^3 - \Delta q_{T_1}^4\right)^2}{T_1} + R_{on} \frac{\left(\Delta q_{T_1}^3 - \Delta q_{T_1}^5\right)^2}{T_1} + R_{on} \frac{\left(\Delta q_{T_1}^7 - \Delta q_{T_1}^4\right)^2}{T_1} \\ &= \left(\frac{85}{64}\right) R_{on} \frac{\left(\Delta q_{V_0}\right)^2}{T} + R_{on} \frac{\left(\Delta q_{T_1}^7 - \Delta q_{T_1}^8\right)^2}{T_2} + \\ R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^2 - \Delta q_{T_2}^4\right)^2}{T_2} + \\ R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^2 - \Delta q_{T_2}^4\right)^2}{T_2} + \\ R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^2\right)^2}{T_2} + \\ R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^2\right)^2}{T_2} + \\ R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^4\right)^2}{T_2} + R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^4\right)^2}{T_2} + \\ R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^4\right)^2}{T_2} + R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^4\right)^2}{T_2} + \\ R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta q_{T_2}^4\right)^2}{T_2} + R_{on} \frac{\left(\Delta q_{T_2}^4 - \Delta$$

From (A43) - (A45), we have the total consumed energy as

$$W_T = \left(\frac{85}{32}\right) R_{on} \frac{\left(\Delta q_{V_o}\right)^2}{T}.\tag{A46}$$

From Eq. (A46), we get  $R_{SC1}$  as  $(85/32)R_{on}$ , because  $W_T$  of Fig. 2 is expressed by Eq. (28). Therefore, the

four-terminal equivalent model of the 1/16× stepdown cascade ladder-type converter can be expressed by the K-matrix as follows:

$$\begin{bmatrix} V_{in} \\ I_{in} \end{bmatrix} = \begin{bmatrix} 16 & 0 \\ 0 & 1/16 \end{bmatrix} \begin{bmatrix} 1 & (85/32)R_{on} \\ 0 & 1 \end{bmatrix} \begin{bmatrix} V_o \\ -I_o \end{bmatrix}.$$

(A47)

Finally, by combining Eqs. (42) and (A47), the characteristics of the conventional hybrid-type 1/48× step-down converter using a ladder-type converter can be obtained as shown in Table 1.