RESEARCH ARTICLE OPEN ACCESS

# VLSI Design of Non-Redundant Radix-4 Signed-Digit Encoding for Pre-Encoded Multipliers

<sup>1</sup>Kalpana Kparaboina, <sup>2</sup>Pabbaraju Padmaja, <sup>3</sup>N.Chandrashekhar

<sup>1</sup>M-Tech, Dept. of ECE Khammam Institute of Technology and Science, Khammam, TS.

<sup>2</sup>M-Tech, Dept. of ECE Khammam Institute of Technology and Science, Khammam, TS.

# **Abstract:**

In this paper, we show an outline of pre-encoded multipliers for cutting edge hail dealing with applications in perspective of separated encoding of coefficients. To this extend, the Non-Redundant radix-4 Signed-Digit (NR4SD) encoding system, which uses the digit regards f1; 0; b1; b2g or f2; 1; 0; b1g, is proposed provoking a multiplier plot with less personality boggling fragmentary things execution. Wide exploratory examination affirms that the proposed pre-encoded NR4SD multipliers, including the coefficients memory, are more zone and power profitable than the consistent Modified Booth plot

**Keywords** — **Modified booth Algorithm**, **Pre-Encoded Multiplier**, **Conventional MBMultiplier**, **Pre-Encoded MB Multiplier**, **VLSI Design**.

### 1. INTRODUCTION

Blended media and propelled signal getting ready (DSP) applications (e.g., snappy Fourier change (FFT), sound/video CoDecs) finish a far reaching number of duplications with coefficients that don't change in the midst of the execution of the application. Since the multiplier is a basic section for executing computationally heightened applications, its designing truly impacts their execution. Consistent coefficients can be encoded to contain the base nonzero digits using the canonic stamped digit (CSD) depiction [1]. CSD multipliers include the minimum non-zero partial things, which along these lines decreases their trading activity. In any case, the CSD encoding incorporates veritable hindrances. Crumbling methodology [2], which diminishes silicon extend by timemultiplexing various operations into single utilitarian units, e.g., adders, multipliers, isn't conceivable as the CSD-based

multipliers are hard-wired to specific coefficients. In [3], CSD-based programmable multiplier setup proposed for social occasions of pre-chosen coefficients that offer certain features. The measure of ROM used to store the social affairs of coefficients is basically decreased and likewise the locale and power use of the circuit. In any case, this multiplier arrangement needs versatility since the inadequate things age unit is delineated especially for a social affair of coefficients and can't be reused for another get-together. Moreover, this system can't be easily extended to huge social affairs of fated coefficients achieving meanwhile high profitability. Balanced Booth (MB) encoding [4], [5], [6], [7] handles the beforehand said imperatives and abatements to a huge bit of the amount of fragmentary things coming to fruition to lessened locale, essential deferral and power Nevertheless, a submitted encoding circuit is

<sup>&</sup>lt;sup>3</sup>Associate Professor& HOD Dept. of ECE Khammam Institute of Technology and Science, Khammam, TS.

required and the midway things age is more mind boggling. In [8], Kim et al. proposed a strategy like [3], for arranging capable MB multipliers for get-togethers of pre-chosen coefficients with comparable controls depicted in the past segment. 2.Non-Redundant Radix-4 Signed-Digit Algorithm

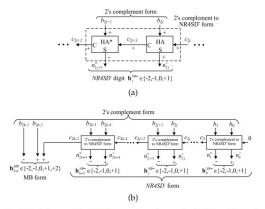

In this portion, we show the Non-Redundant radix-4 Signed-Digit (NR4SD) encoding methodology. As in MB outline, the amount of fragmentary things is diminished to half. When encoding the 2's supplement number B, digits bNR i take one of four regards: f2; 1; 0; b1g or bNRb j 2 f1; 0; b1; b2g at the NR4SD NR4SDb computation, or independently. Only four interesting regards are used and not five as in MB estimation, which prompts 0 j k 2. As we need to cover the dynamic extent of the 2's supplement outline, the most basic digit is MB encoded (i.e., bMB k1 2 f2; 1; 0; b1; b2g). The NR4SDb NR4SD and encoding computations are outlined in detail in Figs. 1 and 2, independently. NR4SD Algorithm

TABLE 1 Modified Booth Encoding

| $b_{2j+1}$ | $b_{2j}$ | $b_{2j-1}$ | $\mathbf{b}_{j}^{MB}$ | $s_{j}$ | $one_j$ | $two_j$ |

|------------|----------|------------|-----------------------|---------|---------|---------|

| 0          | 0        | 0          | 0                     | 0       | 0       | 0       |

| 0          | 0        | 1          | +1                    | 0       | 1       | 0       |

| 0          | 1        | 0          | +1                    | 0       | 1       | 0       |

| 0          | 1        | 1          | +2                    | 0       | 0       | 1       |

| 1          | 0        | 0          | -2                    | 1       | 0       | 1       |

| 1          | 0        | 1          | -1                    | 1       | 1       | 0       |

| 1          | 1        | 0          | -1                    | 1       | 1       | 0       |

| 1          | 1        | 1          | 0                     | 1       | 0       | 0       |

Stage 1. Consider the fundamental regards j ¼ 0 and c0 ¼ 0.

Stage 2. Register the pass on c2jb1 and the total nb 2j of a half snake (HA) with inputs b2j and c2j (Fig. 1a).

Stage 3. Determine the unequivocally stamped pass on c2jb2 (+) and the antagonistically checked aggregate n 2jb1 (-

) of a HA\* with inputs b2jp1 (+) and c2jp1 (+) (Fig. 1a). The yields c2jp2 and n 2jp1 of the HA\* relate to its data sources

Fig. 1. Block diagram of the NR4SD  $^{\!\!-}$  encoding scheme at the (a) digit and (b) word level.

## 3.Pre-Encoded Mb Multiplier Design

In the pre-encoded MB multiplier plot, the coefficient B is encoded separated by the normal MB shape (Table 1). The ensuing encoding indications of B are secured in a ROM. The drifted some segment of Fig. 3, which contains the ROM with coefficients in 2's supplement outline and the MB encoding circuit, is right now totally supplanted by the ROM of Fig. 5. The MB encoding squares of Fig. 3 are prohibited. The new ROM of Fig. 5 is used to store the encoding indications of B and sustain them into the partial thing generators (PPi Generators PPG) on each clock cycle. Centering to lessen trading activity, the regard '1' of sj in the last area of Table 1 is supplanted by '0'. The sign sj is by and by given by the association: hence, the PPG of Fig. 4a is supplanted by the one of Fig. 4b. Appeared differently in relation to (4), (12) prompts a more personality boggling layout. In any case, due to the pre-encoding procedure, there is no zone/concede overhead at the circuit. The fragmented things, weighted, and the COR of (11) are fed into a CSA tree. The data pass on cin; of (11) is figured as cin; 1/4 sj in perspective of (12) and Table 1. The CS yield of the tree is

finally united by a fast CLA wind. In any case, the ROM width is extended. Each digit requests three encoding bits (i.e., s, two and one (Table 1)) to be secured in the ROM. Since the n-bit coefficient B needs three bits for every digit when encoded fit as a fiddle, the ROM width essential is 3n/2 bits for every coefficient. Thus, the width and the general size of the ROM are extended by 50 percent diverged from the ROM of the common arrangement (Fig. 3).

Fig. 4. Generation of the ith Bit p<sub>ji</sub> of PP<sub>2</sub> for a) Conventional, b) Pre-Encoded MB Multipliers, c) NR4SD<sup>+</sup>, d) NR4SD<sup>+</sup> Pre-Encoded Multipliers, and e) NR4SD<sup>+</sup>, f) NR4SD<sup>+</sup> Pre-Encoded Multipliers after reconstruction.

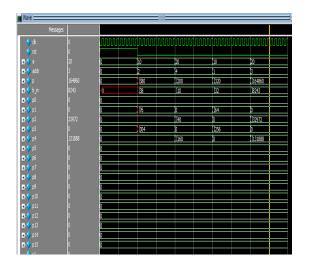

## **4.SIMULATION RESULTS**

**SCHEMATIC**

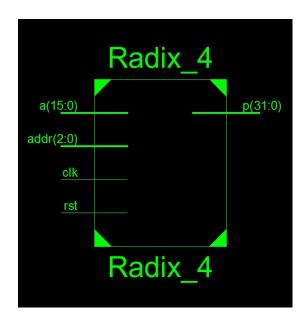

**Block Diagram**

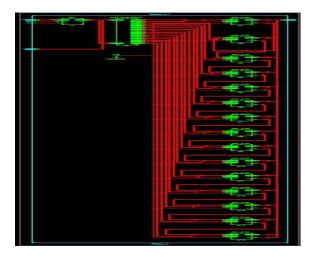

**RTL Schematic**

#### 5.CONCLUSION

In this paper, new blueprints of preencoded multipliers are researched by detached encoding the standard coefficients and securing them in system memory. We propose encoding these coefficients in the Non-Redundant radix-4 Signed-Digit (NR4SD) outline. The proposed pre encoded NR4SD multiplier designs are more area and power capable stood out from the normal and pre-encoded MB plots. Expansive trial examination checks the increments of the

proposed pre-encoded NR4SD multipliers to the extent domain diserse quality and power usage stood out from the customary MB multiplier.

### **6.REFERENCE**

- [1] G. W. Reitwiesner, "Binary arithmetic," Adv. Comput., vol. 1, pp. 231–308, 1960.

- [2] K. K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation, Hoboken, NJ, USA: Wiley, 2007.

- [3] Y.-E. Kim, K.-J.Cho, J.-G.Chung, and X. Huang, "CSD-based programmable multiplier design for predetermined coefficient groups," IEICE Trans. Fundam.Electron.Commun.Comput.Sci., vol. 93, no. 1, pp. 324–326, 2010.

- [4] O. Macsorley, "High-speed arithmetic in binary computers," Proc. IRE, vol. 49, no. 1, pp. 67–91, Jan. 1961.

- [5] W.-C. Yeh and C.-W. Jen, "High-speed booth encoded parallel multiplier design," IEEE Trans. Comput., vol. 49, no. 7, pp. 692–701, Jul. 2000.

- [6] Z. Huang, "High-level optimization techniques for low-power multiplier design," Ph.D. dissertation, Dept. Comput. Sci., Univ. California, Los Angeles, CA, USA, 2003.

- [7] Z. Huang and M. Ercegovac, "High-performance low-power left-to-right array multiplier design," IEEE Trans. Comput., vol. 54, no. 3, pp. 272–283, Mar. 2005.

- [8] Y.-E. Kim, K.-J.Cho, and J.-G. Chung, "Low power small area modified booth multiplier design for predetermined coefficients," IEICE Trans. Fundam. Electron.Commun.Comput. Sci., vol. E90-A, no. 3, pp. 694–697, Mar. 2007.

#### **Authors Profiles**

KALPANA KPARABOINApursuing M-Tech (VLSI system design)Degree from Khammam Institute of Technology and Science(JNTU HYDERABAD), Ponnekal, Khammam, in (2015-2017) 2017, and B-Tech Degree from SwarnaBharathi College Of Engineering (JNTU HYDERABAD), Thanikella , Khammam,in( 2008-2012) 2012, all in Electronics and Communication Engineering.

PABBARAJU PADMAJApursuing M-Tech (ES)Degree from MITS(JNTU HYDERABAD), Kodada, Nalgonda, in (2009-2011) 2011, and AMIE in ECE from Institution of Engineers(India) in 2002.

**Page 448**

**N.CHANDRASHEKHAR**completed his M-Tech with electronics and communication engineering. He has published more than five international journals. Currently he is a research Scholar in JNTU, Hyderabad and working as Associate Professor & Head of the department for ECE in Khammam Institute of Technology and Science

.