RESEARCH ARTICLE OPEN ACCESS

# A MODIFIED TWO SWITCHED-INDUCTOR QUASI Z-SOURCE INVERTER

V.Malathi<sup>1</sup>

1(Department of EEE, SCSVMV University, Enathur, Kanchipuram)

### Abstract:

In this paper, the technique of bootstrap capacitor is applied to the (cSL-qZSI) topology to improve its features such as increasing its total gain and minimizing the total stress across the used component Using switched inductor principle has improved the boosting gain of the applied topology at the same shoot through duty cycle (D) compared with the convention one. This also leads to operate at higher modulation index (M) and so low stress over the components is resulted. Switched inductor cell is applied to classic qZSI topology instead of the two main inductors to give anew topology that has been called a continuous input current switched inductor quasi Z-Source Inverter (cSL-qZSI)

Keywords-- Z source inverter, bootstrap capacitor, Voltage gain

### I. INTRODUCTION

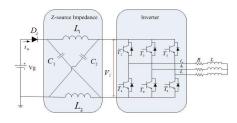

In 2002, a single stage inverter called Z-Source Inverter (ZSI), shown in Fig. 1, has been proposed to overcome the limitations traditional voltage source inverter (VSI) and the traditional current source inverter (CSI) [1] - [4]. ZSI utilizes shoot-through zero state where two switches in the same leg or all switches are gated on simultaneously to boost the output voltage. In ZSI, the six permissible active switching states of VSI remains unchanged; and the zero states can be partially or completely replaced by the shoot-through states depending on the desired boosting voltage. However, these topologies of ZSource Inverter have some limitations, such as small boost factor, high voltage stress across the switches and capacitors and huge inrush current. Several improvements of the basic ZSI topology have been recently developed to overcome these limitations and to improve its features [5]-[9]. Also, the concept of the switched inductor (SL) technique [10] has been integrated into the classical Zsource impedance network; consequently a new SL Z-source impedance network topology has been

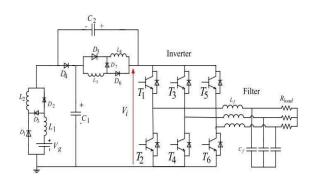

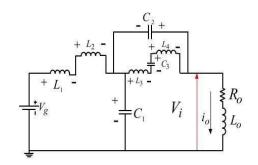

obtained [11]. Using switched inductor principle has improved the boosting gain of the applied topology at the same shoot through duty cycle (*D*) compared with the convention one. This also leads to operate at higher modulation index (*M*) and so low stress over the components is resulted. Switched inductor cell is applied to classic qZSI topology instead of the two main inductors to give anew topology that has been called a continuous input current switched inductor quasi Z-Source Inverter (cSL-qZSI) [12], as shown in Fig. 2. Recently, a bootstrap capacitor is used to replace the middle diode in the switched cell; and it is applied to one switched inductor (qZSI) [13].

Fig. 1. Classical Z-Source inverter (ZSI)

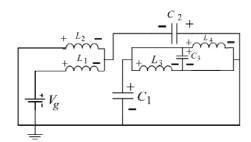

In this paper, the technique of bootstrap capacitor is applied to the (cSL-qZSI) topology to improve its features such as increasing its total gain and minimizing the total stress across the used component. The proposed topology is presented in section II. Then, the theoretical analysis is explained in details in section III. A comparison with the classic one (cSL-qZSI) is explained in section IV; afterward the simulation results are given in section V and the experimental set-up including their results are illustrated in section VI. Lastly the conclusion is given in section VII. duty cycle (D) and modulation index (M). From cost point of view, the capacitor is less expensive than the diode; and from

Fig. 2.Classical cSL-qZSI topology.

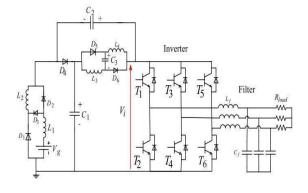

Fig.3.The proposed topology (MTSL-QZSI).

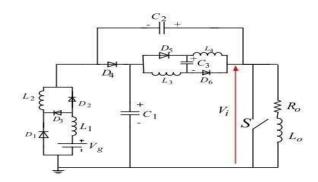

Fig. 4. Equivalent circuit of the proposed topology

### II. THE PROPOSED TOPOLOGY

The proposed topology is shown in Fig. 3. The construction of the proposed topology is similar to the cSLqZSI topology; the main difference in the construction between them is the replacement of the diode in the second switched cell (*D7*) with a bootstrap capacitor (*C3*) without increasing the number of component in the circuit.

It contains four inductors (L1, L2, L3, L4), three capacitors (C1, C2,C3) and six diodes (D1, D2, D3, D4, D5, D6). The proposed topology (MTSL-QZSI) has the merits of continuous input current drawn from the DC source due to the direct connection between the inductor (L1) and the DC voltage source (Vg); and it has a common mode connection between the DC source and the inverter bridge.

# III. THEORETICAL ANALYSIS OF THE PROPOSED TOPOLOGY

Due to the balancing of output AC load, the inverter side can be presented as equivalent R-L load; and the equivalent circuit of the proposed topology (MTSL-qZSI) is shown in Fig. 4. Furthermore, the operating states are simplified into shoot-through state when the switch (S) is on and non shoot through state when the switch is off.

Besides, all the analysis will be done under the following assumptions:

• The current of the four inductors operates in

Continuous Conduction Mode (CCM).

• All components are ideal.

The voltages across the *L*<sub>1</sub>, *L*<sub>2</sub>, *L*<sub>3</sub>, *L*<sub>4</sub>, *C*<sub>1</sub>, *C*<sub>2</sub> and *C*<sub>3</sub> are *VL*<sub>1</sub>, *VL*<sub>2</sub>, *VL*<sub>3</sub>, *VL*<sub>4</sub>, *VC*<sub>1</sub>, *VC*<sub>2</sub> and *VC*<sub>3</sub>, respectively. The polarity of these voltages remain the same in the shoot through state and non-shoot through state to simplify the analysis of the circuit. The period of shoot through state is (*DT*) and the period of non-shoot through state is (*1-D*)*T* where *T* is the switching cycle and *D* represents the duty ratio of the shoot through for each cycle.

### A.Non Shoot-Through State

As shown in Fig. 5, during this state, the diodes D1, D2, D5 and D6 are turned off, whereas the diodes D3 and D4 are in conducting mode. The inductors L1 and L2 are connected in series; whereas L2, L3, and C3 are also connected in series. L1, L2, L3, L4 and C3 are discharged and transfer energy from the DC source to the load whereas C1 and C2 start to charge,

Thus the following equation can be obtained,

$$V_{L1} + V_{L2} = (V_g - V_{C1})$$

$$V_{L3} + V_{L4} = (V_{C3} - V_{C2})$$

$$V_i = (V_{C1} + V_{C2})$$

(1)

Where,  $V_i$  represents the peak DC link voltage.

$$V_{L1} = (V_g + V_{C2})$$

$$V_{L2} = V_{C2}$$

$$V_{L3} = V_{L4} = V_{C3} = V_{C1}$$

(2)

$$V_{C3} = \left(\frac{1 - 2D - 3D^2}{1 - 2D + D^2}\right) V_{C2} - \left(\frac{2D}{1 - 2D + D^2}\right) V_g$$

$$V_{C3} = \left(\frac{1 - D}{1 + D}\right) V_{C2}$$

(6)

### Equation (2) can be rewritten as:

$$V_{L1} + V_{L2} = (V_g + 2V_{C2})$$

$$V_{L3} + V_{L4} = 2V_{C3} = 2V_{C1}$$

(3)

From (1) and (3) and based on the voltage second balance principal for the inductors L1, L2, L3 and L4, yields,

By solving (4), obtained,

$$V_{C1} = \left(\frac{1}{1-D}\right) \left(2DV_{C2} + V_g\right)$$

$$V_{C3} = \left(\frac{1-D}{1+D}\right) V_{C2}$$

$$V_{C1} = \left(\frac{1-D}{2D}\right) \left(V_{C2} - V_{C3}\right)$$

(5)

By reduction (5) leads to,

Then, equation (6) yields to,

$$V_{C2} = \left(\frac{1+D}{1-4D-D^2}\right) V_g \tag{7}$$

By Substituting (7) into (5); the capacitor voltage V c1 is

By Substituting (7) into (5); the capacitor voltage V c1 is

$$V_{C1} = V_{C3} = \left(\frac{1 - D}{1 - 4D - D^2}\right) V_g \tag{8}$$

So the peak DC link voltage can be obtained by Substituting

(7) and (8) into (1),

(7) and (8) into (1),

$$V_{i} = \left(\frac{2}{1 - 4D - D^{2}}\right) V_{g} \tag{9}$$

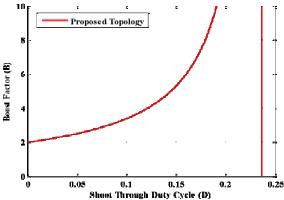

Subsequently, the boost factor (B) which represents the ratio between the peak DC link voltage (Vi) and the DC source voltage (Vg) can be presented as:

$$B = \frac{V_i}{V_g} = \frac{2}{1 - 4D - D^2} \tag{10}$$

Also, the total gain (G) of the proposed topology can be written as:

$$G = BM = \frac{2M}{1 - 4D - D^2} \tag{11}$$

Where M represents the modulation index.

It worth to mentioned that, the above equations are valid only in the case of boosting mode where shoot through duty cycle is larger than zero (D>0). Else, the following equation is valid:

$$V_{C1} = V_g V_{C2} = V_{C3} = 0 V_i = V_g$$

(12)

According to (11), the proposed topology has

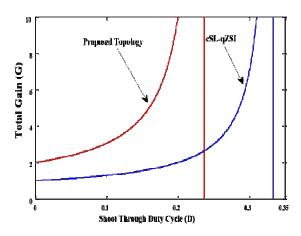

larger boost factor at small value of shoot through duty cycle where theoretically it equals to infinity value at D=0.24 as shown in Fig. 7.

Fig.7. Boost Factor (B) versus Shoot Through Duty Cycle (D).

Fig.8. Simple boost control technique.

Fig. 9 Total Gain (G) versus shoot through Duty Cycle (D) for the proposed topology versus the conventional cSL-qZSI topology.

# IV. COMPARSION QZSITOPOLOGY

WITH CSL-

topology. On the other gain (G), so the proposed topology give an improvement in the

The comparison between the proposed topology (MTSLqZSI) and the classic one (cSL-qZSI) can be organized from the following points of view,

### A.The boost ability

The boost factor of (cSL-qZSI) can be expressed as [12],[14]

By applying the same PWM control methods to generate the shoot through duty cycle of the two topologies; if they

have the same shoot through duty cycle (*D*), they will have the same modulation index (*M*), but the MTSL-qZSI has larger boost factor (*B*) than cSL-qZSI so it has the largest total gain as shown in Fig. 9.

Thus, to obtain the same total gain (G) from the two topologies, (MTSL-qZSI) topology requires a smaller shoot through duty cycle (D) than with (cSL-qZSI) topology, this leads to the proposed topology to operate at higher modulation index (M) which improves the performance of the topology in reduction the total harmonics distortion in the output of the inverter. Therefore, a low size filter is used to get sinusoidal output voltage.

## **B.**Voltage Stress

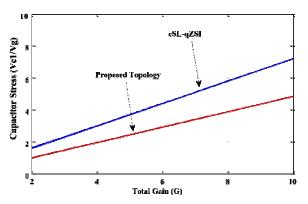

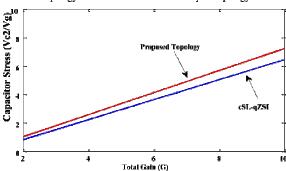

The voltage stress across the used capacitor effect on the cost of the system where larger voltage stress requires using a capacitor that can withstand that high voltage stress across it and this will be costly [15]. As a larger gain is obtained with small shoot through, the voltage stress across the used capacitors and switched devices may be smaller. The voltage across the capacitor C1 and

$C_2$ for (cSL-qZSI) topology can be written as [12], As shown in Fig.10, at the same total gain (G) the stress across the capacitor  $C_I$  is smaller for the proposed topology compared to cSL-qZSI

Fig. 10. Voltage stress across C1 versus the total gain (G) for the proposed topology versus the conventional cSL-qZSI topology.

$\label{eq:Fig.11.Voltage} Fig.11. \ Voltage \ stress \ across \ C2 \ versus \ the \ total \ gain \ (G) \ for \ the \\ proposed \ topology \ versus \ the \ conventional \ cSL-Qzsi \ topology.$

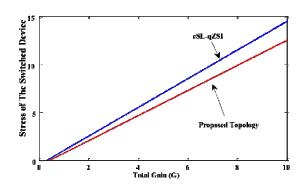

In Fig. 12; it is obviously that at the same total gain, the voltage stress  $V_S$  across the switched devices (IGBTs) for the proposed topology is smaller than that for cSL -qZSI topology. This can be explained as it requires small shoot

through duty cycle (D) to give the same total gain, so it has larger modulation index (M). So, the proposed topology has more freedom in selecting the switched devices rating compared to cSL-qZSI.

#### V. SIMULATION RESULTS

Simulation under PSIM program has been performed to validate the feasibility of the proposed topology. The simulation is applied to the proposed topology based on the parameters listed in Table I.

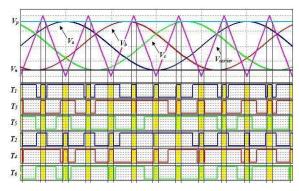

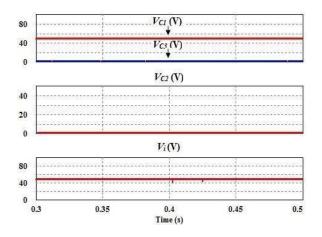

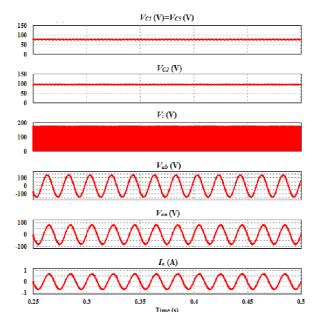

Firstly, the simulation work is implemented with shoot through duty cycle at D=0.1. According to (7) to (11) and (13), the following values can be evaluated at D=0.1:0.9, B= 3.389, G= 3.05,Vi= 169.5V, VCI= 76.27V,

VC2=93V, VC3=76.27V, Van (rms) = 53.9V, Vab (rms) = 93.4V and Ia (rms) = 0.49A.The simulations results are presented in Fig. 13, where the capacitor voltages VC1 and VC3 have the same value of 78V, the capacitor voltage VC2 equals 96V, the peak value of DC —link voltage Vi equals 174V, the rms value of line voltage equals 100 V, the rms value of phase voltage equals 57.7V and the rms value of output load current equals 0.52A.

Secondly, simulation work is performed at D = 0 to show the validation of (12) and the following values can be calculated at D = 0:

M= 1, B= 1, G= 1,  $V_i=$  50V,  $V_{C1}=$  50V,  $V_{C2}=V_{C3}=$  0V. The simulations results are presented in Fig. 14, where the

Fig. 14. Simulation results at D=0.

Capacitor voltages VC1 equals 50V, the capacitor voltage VC3 equals 0 V, the capacitor voltage VC2 equals 0V, the peak value of DC-link voltage Vi equals the value of the input DC source 50V.

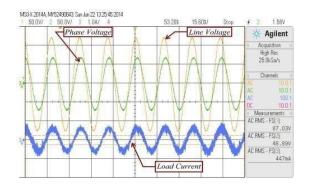

### VI. EXPERIMENTAL RESULTS

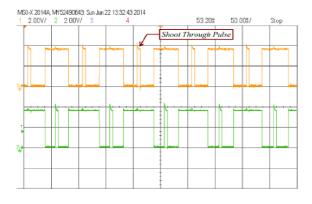

The experimental work is carried out for the proposed topology with the same parameters applied in the simulation test. The control is developed using the digital signal processing kit TMDSCNCD28335 which is linked with PSIM program. A laboratory prototype for the proposed topology (MTSL-qZSI) is constructed and the experimental setup is shown in Fig. 15. The shoot through duty cycle (D) for experimental work is taken as the same value of shoot through duty cycle in simulation work D=0.1. Also, the firing scheme from the control kit before the gate

drive circuit for upper and lower switch in one phase leg of the inverter is shown in Fig.16.

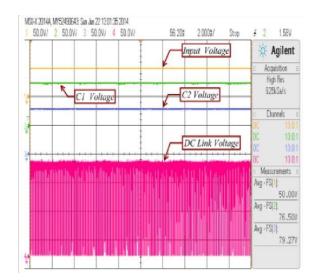

The measurements for DC side of MTSL-QZSI are shown in Fig. 17 where the input voltage of the DC source equals 50V, the voltage across the capacitor  $C_1(VC_1)$  equals 76.5V, the voltage across the capacitor  $C_2(VC_2)$  equals 79.27V and the peak DC link voltage  $(V_i)$  equals 155.5V. The measurements for AC side are shown in Fig. 18 where the rms value of line to line voltage  $(V_{ab})$  equals 87V, the rms value of phase voltage  $(V_{an})$  equals 48.89V and the rms value of load current equals 447mA. There is a slightly difference between the theoretical results and experimental results due to the parasitic impedances for the used components.

Fig. 16. Firing pulses for the two switches of one phase.

Fig.17. DC side measurements.

Fig. 18. AC side measurements

### VII. CONCLUSION

This paper presents a modified topology for the development of the features of Z-source Inverter (ZSI) as a single stage inverter. The principal of the proposed topology depends on using the idea of bootstrap capacitor instead of the middle diode in the second switched cell in the continuous two switched inductor quasi ZSI (cSL- qZSI) topology. It can be summarized the following advantages for the proposed topology (MTSL-qZSI):

Larger boost factor (B) than any other topology that related with Z-source Inverter field, up till now.

- ✓ Continuous input current drawn from the source.

- ✓ Common mode feature.

- Slightly improving in capacitor stress compared to similar classic one cSL-qZSI.

Obtaining larger gain with short shoot through lead to operating at higher modulation index (M) which results in reducing the stress on the switched devices and improving the total harmonic distortion for the inverter output so, low size output filter is required. Improving in conversion efficiency due to

using the capacitor instead of the diode compared to cSL-qZSI.

Therefore, the above advantages allow the proposed topology (MTSL-qZSI) to be widely used as an inverter topology.

#### REFERENCES

- [1] F. Z. Peng, "Z-Source Inverter," IEEE Trans. Ind. Applicat., vol. 39,

- no. 2, pp. 504-510, Mar./Apr. 2003.

- [2] F.Z. Peng, X. Yuan, X. Fang and Z. Qian, "Z-source inverter for adjustable speed drives," Power Electronics Letters, IEEE 1.2, pp.3335, 2003.

- [3] Y. Huang, M. Sheng and F.Z. Peng, "Z-source inverter for residential photovoltaic systems," IEEE Trans. Power Electron, pp.1776-1782, 2006.

- [4] T. Bülo, B. Sahan, C. Nöding and P. Zacharias, "Comparison of threephase inverter topologies for grid-connected photovoltaic systems," In Proc. 22nd Eur. Photovolt. Sol. Energy Conf. Exhib., Milan, Italy, Sep. 2007.

- [5] F. Gao,P.C.Loh, D.Li and F. Blaabjerg, "Asymmetrical and symmetrical embedded Z-Source inverters," Power Electronics, IET , vol.4, no.2, pp.181-193, Feb. 2011.

- [6] R. Strzelecki, M. Adamowicz, N. Strzelecka and W. Bury,"New type TSource inverter," In Proc. IEEE Compatibility and Power Electronics, CPE'09, pp. 191 195, 2009.

- [7] M. Adamowicz and N. Strzelecka,"T-source inverter," Electrical

- Review, ISSN 0033-2097, vol. 85, no. 10, pp.1-6, 2009.

- [8] W. Qian, F. Z. Peng and H. Cha, "Trans-Z-source inverters," In Proc.

- IEEE Int.Power Electronics Conference IPEC, pp. 1874 1881, 2010.

- [9] M. Adamowicz and R. Strzelecki, "Boost-buck inverters with cascaded qZ-type impedance networks, "Electrical Review, ISSN 0033-2097, vol. 86n. 2, pp.370-375, 2010.

- [10]M. Zhu, K. Yu, and F. L. Luo, "Switched inductor Z-source inverter,"

- IEEE Trans. Power Electron., Vol. 25, No. 8, pp. 2150-2158, Aug. 2010.

- [11]M.K. Nguyen, Y. C. Lim and G. B. Cho," Switched-inductor

- quasiZsource inverter," Power Electronics, IEEE Transactions on,

- 26.11, pp.3183-3191, 2011.

- [12] M. K. Nguyen, Y. C. Lim and J. H. Choi, "Two switched-inductor quasiZ-source inverters," *IET Power Electronics* 5.7, pp.1017-1025, 2012.

- [13]K. Deng, J. Zheng and J. Mei, "Novel Switched-Inductor Quasi-

- Zsource Inverter," Journal of power Electronics, 14(1), pp. 11-21, 2014. [14]F.Z.Peng and Miaosen Shen, Zhaomingian, "Maximum Boost

- Control of the Z-source Inverter,' IEEE Transactions on Power

- Electronics, vol.20, No.4, pp.833-838, 2005.

- [15]Y. Tang, S. J. Xie, C. H. Zhang, and Z. G. Xu, "Improved Z-source inverter with reduced Z-source capacitor voltage stress and softstart capability," IEEE Trans. Power Electron., Vol. 24, No. 2, pp.409415, Feb.