# **Role of Compilers in Computer Architecture**

Jasveen Kaur, Amanpreet Kaur

Assistant Professor, Guru Nanak Dev University, jasveeen kaur.1990@gmail.com

**Abstract** -- A compiler is a software layer that helps the high level executions that are made in a programming language to be compiled and implemented by the underlying hardware computer architecture. Though a compiler is majorly designed based on the language specification, the hardware that it is going to implement on has a significant role in the compiler design. Effective compilers allow for a more efficient execution of application programs for a given computer architecture, while well-conceived architectural features can support more effective compiler optimization techniques. A well thought-out strategy of tradeoffs between compilers and computer architectures is the key to the successful designing of highly efficient and effective computer systems. From embedded micro-controllers to large-scale multiprocessor systems, it is important to understand the interaction between compilers and computer architectures. The factors in which the compiler and the computer architecture have to agree on are: regularity, orthogonality and compensability. Any issue with these factors result in a tougher task for the compiler designer. So, making an efficient compiler involves the collaborative work of both a compiler designer and the hardware architects who built the computer architecture.

**Keywords** – Compiler, HLL(High Level Language), Compiler optimization, Cost equation, Regularity, Orthogonality, Compensability

#### INTRODUCTION

Today almost all programming is done in high-level languages for desktop and server applications. In earlier times for these applications, architectural decisions were often made to ease assembly language programming or for a specific kernel. Because the compiler will significantly affect the performance of a computer, now a days, understanding compiler technology is critical to design and efficient implementation of an instruction set. Once it was popular to try to isolate the compiler technology and its effect on hardware performance from the architecture and its performance, just as it was popular to try to separate architecture from its implementation. This separation is essentially impossible with today's desktop compilers and computers. Architectural choices affect the quality of the code that can be generated for a computer and the complexity of building a good compiler for it, for better or for worse. In this section, we discuss the critical goals in the instruction set primarily from the compiler viewpoint. It starts with a review of the structure of current compilers. Next we discuss how compiler technology affects the decisions of the architect, and how the architect can make it hard or easy for the compiler to produce good code.

This paper focuses on listing the structure of a compiler and the underlying architecture, the mutual dependency between them and how the efficiency can be increased by several factors that are modified in the compiler level and also in the architectural level. Next we discuss what is compiler, hardware compilation, impact of optimizations on performance, the Impact of Compiler Technology on the Architect's Decisions, Factors in architecture that affect the compiler optimization

# 1.1 What is a Compiler?

Over the years, the use of higher level languages for programming(HLLs) has become widespread. In the last two decades two other factors, namely portability and maintainability of programs have come up leading to the development of programming languages with more powerful features. However computers do not understand HLLs. So a programmers view of the execution of his program cannot be realized in practice. So in order to execute an HLL program written by a programmer it is necessary to convert it into a language understandable by a machine which is called as machine language. A translator is a program which performs translation from HLL into the machine language of computer. It also performs diagnostics i.e error detection.

# 1.2 Structure of Compiler

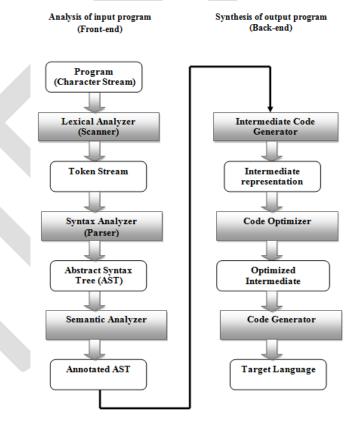

The structure of the compiler can be classified as front end and backend in which the last one is more dependent on the architectural framework of the system. The front end consists of the Lexical Analyzer, Syntax Analyzer and Semantic Analyzer.

**Lexical Analyzer:** It isolates each part of the statement and tokenizes them as operands, operator, variable, constants etc. The lexical analysis phase reads the characters in the program and groups them into tokens that are sequence of characters having a collective meaning.

Syntax Analyzer: It parses the token sequence and identifies the syntactic structure of the program.

Semantic Analyzer: This phase of the compiler checks for type errors and adds all the necessary semantic information to the parse tree.

The back end consists of the Intermediate Code Generator, Code Optimizer and Code Generator.

**Intermediate Code Generator:** This phase of compiler transforms parser tree into an intermediate language representation of the source program. Intermediate codes are machine independent codes, but they are close to machine instructions.

**Code Optimizer:** Code optimization is the process of modifying the working code to a more optimal code based on a particular goal. The code optimization phase attempts to improve the intermediate code, so that faster running machine code will result.

**Code Generator:** It takes the optimized intermediate representation of the source program as input and produces a target program or object program as its output. The final

phase of the compiler is the generation of the target code or machine code or assembly code. Memory locations are selected for each of the variables used by the program. Then intermediate instructions are translated into a sequence of machine instructions that perform the same task.

The back end performs the intermediate code generation, code optimization and generation which are very significant parts in the compilation process.

Figure 1: The Complete Structure of a compiler.

# 1.3 Overview of compilation process

The process of translating from on language to another is composed of two important phases:- (1) analysis of the source text, and (2) synthesis of the target text. This model of translation is very general. In order to apply this model to translation from an HLL to machine language, we must determine the component subtasks for analysis/synthesis and consider their design pre-requisites.

In the analysis phase, we are concerned with determining he meaning of a Source language text. In other words we must know the grammar of the source language. Also we should know how to determine the statement once its grammatical structure is revealed. In the terminology of translators we call the rules of grammar and the rules of meaning as syntax and semantics of the language respectively.

In order to fulfill the task of compilation we need to find out something more than merely meaning of the source program. We should find out what particular instructions and what addressing modes we should use in the target program to perform the above steps. Such aspects of compilation concerned with the nature of target machine are known as the pragmatics of compilation. Thus if we consider different compilers for an HLL, we find that the semantics used by them are identical while the pragmatics used by them are different. For this reason we associate the term semantics with programming language and the term pragmatics with the compiler. Pragmatics of a compiler would be used during the synthesis phase, to determine how to reflect the meaning of a source language program into target program.

Analysis + Synthesis = Translation

# 1.4 The Structure of Recent Compilers:

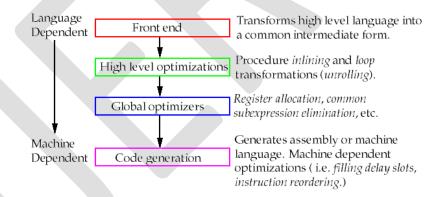

The figure below shows the structure of recent compilers. In this figure compilers typically consist of two to four passes or phrases, with more highly optimizing compilers having more passes. This structure maximizes the probability that a program compiled at various levels of optimization will produce the same output when given the same input. The optimizing passes are designed to be optional and may be skipped when faster compilation is the goal and lower-quality code is acceptable. A pass is simply one phase in which the compiler reads and transforms the entire program. Because the optimizing passes are separated, multiple languages can use the same optimizing and code generation passes. Only a new front end is required for a new language.

Figure 2: Structure of recent compilers

A compiler writer's first goal is correctness—all valid programs must be compiled correctly. The second goal is usually speed of the compiled code. Typically, a whole set of other goals follows these two, including fast compilation, debugging support, and interoperability among languages. Normally, the passes (phrases) in the compiler transform higher-level, more abstract representations into progressively lower-level representations. Eventually it reaches the instruction set. This structure helps manage the complexity of the transformations and makes writing a bug-free compiler easier.

The complexity of writing a correct compiler is a major limitation on the amount of optimization that can be done. Although the multiple-pass structure helps reduce compiler complexity, it also means that the compiler must order and perform some transformations before others. In the diagram of the optimizing compiler in Figure 2 above, we can see that certain high level optimizations are performed long before it is known what the resulting code will look like. Once such a transformation is made, the compiler can't afford to go back and revisit all steps, possibly undoing transformations. Such iteration would be prohibitive, both in compilation time and in complexity. Thus, compilers make assumptions about the ability of later steps to deal with certain problems.

For example, compilers usually have to choose which procedure calls to expand inline before they know the exact size of the procedure being called. Compiler writers call this problem the *phase-ordering problem*.

How does this ordering of transformations interact with the instruction set architecture? A good example occurs with the optimization called *global common sub-expression elimination*. This optimization finds two instances of an expression that compute the same value and saves the value of the first computation in a temporary. It then uses the temporary value, eliminating the second computation of the common expression.

For this optimization to be significant, the temporary must be allocated to a register. Otherwise, the cost of storing the temporary in memory and later reloading it may negate the savings gained by not re-computing the expression. There are, in fact, cases where this optimization actually slows down code when the temporary is not register allocated. Phase ordering complicates this problem because register allocation is typically done near the end of the global optimization pass, just before code generation. Thus, an optimizer that performs this optimization must assume that the register allocator will allocate the temporary to a register.

Optimizations performed by modern compilers can be classified by the style of the transformation, as follows:

High-level optimizations are often done on the source with output fed to later optimization passes.

Local optimizations optimize code only within a straight-line code fragment (called a basic block by compiler people).

**Global optimizations** extend the local optimizations across branches and introduce a set of transformations aimed at optimizing loops.

**Register allocation** associates registers with operands.

Processor-dependent optimizations attempt to take advantage of specific architectural knowledge.

# THE IMPACT OF COMPILER TECHNOLOGY ON THE ARCHITECT'S DECISIONS:

The interaction of the compiler and the high level language majorly depends on what instruction set architecture it works on. To have an understanding of how the variables are allocated and addressed and the number of registers used for it can be obtained on looking into the ways how high level language allocate their data:

**Stack** – used for local variable allocation which is referenced in case of procedure call or return and does not push or pop as it is used only as activation records.

Global data area – for global variables or constants and other data structures as arrays

**Heap** – for dynamic objects which do not fit in stack and they are accessed using pointers. The concept of register allocation that we earlier found as optimization technique is suitable for stack allocated objects than the other two. For heap objects it is impossible as a pointer is

used to access it. Some compilers may not allocate register to any local variable if any one of them is addressed by a pointer fearing for its dependency factors.

## FACTORS IN ARCHITECTURE THAT AFFECT THE COMPILER OPTIMIZATION:

Generally the major factor affecting the compiler optimization is the machine on which the code is to be executed because of which few compilers like *gcc* machine description parameters that can be altered have based on the machine in which the compiled code is to be executed.

## **Number of CPU Registers**

The more the number of registers, it makes it easier for the compiler to allocate registers. The local variables will be allocated registers instead of a stack data representation and other intermediate values can also be stored in registers. Here, it is to be noted that RISC uses the multiple register set as any instructions has to be from/to the internal registers but the CISC uses only a single register set as it can address operands directly from the memory bypassing the registers.

#### **RISC vs. CISC**

The CISC (Complex Instruction Set Computers) has a 200 to 250 instructions and has a variable length instructions and addressing modes because of which ends up providing a large case analysis for the instructions to be chosen. Even for simple function it provides several choices and the decision making part for choosing the best instruction out of it makes the compilation speed to slow down. But

250 <u>www.ijergs.org</u>

in RISC (Reduced Instruction Set Computers) which typically has only 20 to 30 most commonly used instructions has a fixed length of instructions and also only specific addressing modes. Any instruction has to pass through the internal registers unlike CISC which references directly to the memory for operands. The compiler has relative cost criteria based on which it chooses the necessary ISA (Instruction Set Architecture).

## **Pipelines**

An instruction can have several execution stages in code generation in which it can be of stages: instruction decode, address decode, memory fetch, register fetch, compute, register store etc. Pipelining comes into picture when one instruction is in memory fetch stage and the other instruction is in register store stage and that they happen to be inter-dependent similar to a deadlock condition. Pipeline conflicts can lead to pipeline stalls which can be reduced by scheduling or re-ordering the instructions.

## **Number of Functional Units**

Some of the architectures have several Arithmetic and Logical Unit (ALU) and Floating Point Unit (FPU) which process certain instructions from a program simultaneously. Analogous to the pipeline conflicts the instructions may be inter-dependent which can also be eliminated by proper instruction scheduling to different units of the CPU.

## Cache Size and type

The cache size that is available in current architectures is 256 KB to 12 MB and type is directly mapped, fully associative. Techniques like inline expansion and loop unrolling require more cache space and may increase the length of code which may have trouble in fitting into the cache memory available. At time due to cache collisions which occur as it is not fully associative will make the available cache memory unproductive at the code execution time.

# Cache/Memory transfer rates.

The compiler is indicated of the issue occurred because of cache collisions or unusability of the cache memory. This may cause efficiency issues in some specialized applications.

#### **WULF's VIEWS:**

William A. Wulf published a paper on the relationship between Computer architecture and compilers in July 1981 which includes some of the principles that were evolved to architectural changes that can simplify the work of the compiler and provide much efficient object code. In this paper, the author discusses a cost equation evaluating the efficiency and cost factors that are taken to consideration from the perspective of the compiler and the architecture.

#### **Cost Equation**

The author classifies the cost based on the software or the compiler design and the hardware i.e. computer architecture part.

Based on the compiler related costs:

- Designing compilers

- Executing the compiler

- Executing the compiled program

In the above listed costs, the designing part is a one-time cost which is high in comparison to the hardware cost. The last two costs are difficult to be related acquisitively but any flaw with it may result in decreased productivity, unavailable functionality and a fall in reliability.

- Based on the computer architecture costs

- Designing the hardware architecture

- •Designing the hardware implementation for the architecture

- Manufacturing the hardware

In the above listed costs, the replication of the designed implementation or in other words the manufacturing of the hardware is the only cost that has been reducing over years. The designing cost is always more as the critical part of the whole architecture is the designing and the one-time work if any irregular structure occurs then it keeps repeating as the implementation is only replicated from the initially designed flawed architecture which would turn expensive if not corrected at design level.

## **GENERAL PRINCIPLES:**

## Regularity

The principle of regularity states that any process if done in one way in one part of the program, then it should be done in the same way whenever the process is done. This is called "the law of least astonishment" in the computer design community. The author applauds that regularity is used in most of the architectures as they accept several different data types and the ability of the compiler to treat the source and destination same way just like how the memory and registers can be treated alike. The irregularities that he complains are about the arithmetic shift and the "immediate mode" arithmetic.

## **Orthogonality**

The feasibility to do a clear lexical analyzing on the machine code i.e., any instruction should provide a clear view of the function, the operands or constants involved in the process.

Some machines provide different instruction sets to memory-to memory, register-to-memory, and register-to-register operations which offers a large case analysis for the compilers to choose from. At times the instruction to be chosen also depends on the addressing mode chosen by the instruction.

## Compensability

The proper usage of the regularity and orthogonality without any deviation will automatically provide compensability i.e., the ability to compose the orthogonal and regular notions in arbitrary ways. The author identifies the root of the problem as the programming languages views data type as a property of data whereas the machine language views data type as a property of operator. Due to this problem, any data type cannot be used from any addressing mode which is viewed as a violation of the composability principle.

## **Other Principles:**

#### One vs. All

Any instruction must be provided with one possible way to do it or all possible ways to do it. For example, if the instruction may appear in 6 possible scenarios, the instruction set must provide one solution for all or 6 possible solutions which will reduce the work of the compiler by just routing it to the specific case or general case. Instead if there exist instruction sets for the instruction, the compiler will have a tough time deciding which scenario the instruction has to be put in. Thus, either one or all will simplify the work of the compiler.

## **Provide primitives, not solutions**

The author states that it is better to provide primitive conclusions from which the programs can synthesis its own solution. The complicated functions as procedure call or case statements the instruction set provided seem to suit few languages well but end up giving a semantic clash with other languages. This is because of providing too much of semantic content to the instruction because of which the compiler can only use those instructions in specific contexts.

#### Addressing

The addressing computations are paths and are not specific to array or other data structures. The referencing from a memory or through pointers appears more complex than it can be which reduces the scope and context in which they can be used.

**Environment Support** The handling of run-time environment issues is the environment support expected from the architecture from the compiler's view. Some run-time environment issues are stack frames, displays or static/dynamic links, exceptions, processes etc. The common run-time issues that need support are: (a) Uninitialized variables (b) Constraint checks (c) Exceptions (d) Debugging support

## **Deviations**

Only in cases where the instructions are implementation independent, the deviation of these principles should occur.

## HOW ARCHITECT CAN HELP COMPILER WRITER?

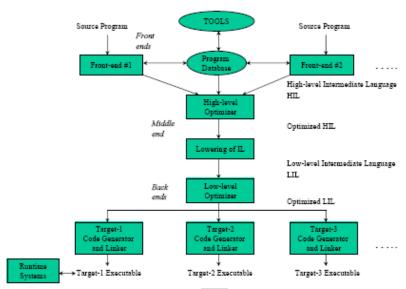

**Figure 3: Structure of Optimizing Compilers**

Today, the complexity of a compiler does not come from translating simple statements like A = B + C. Most programs work fine for simple translations. The complexity arises with large programs and globally complex in their interactions. The structure of compilers chooses the best instruction for the given statement in a small fraction of time. Compiler writers usually work based on a goal where the quality is highly tested for the most frequent instructions and the accuracy is aimed at for the infrequent and complicated instructions. They consider the simple instructions to be available fast and the complex instructions though slow should give accurate results. Some instruction set properties help the compiler writer and makes it easier to write a compiler that will generate efficient and correct code.

**Providing regularity**—it is important to remember that in any instruction set, the influencing factors are the operation, the data type used for the variables and the addressing mode used to call the variable must be orthogonal. In this context orthogonality more about not being inter-dependent on each other i.e., irrespective of the chosen data type any addressing mode can be used should be the condition. For example, the addressing modes and operations are orthogonal if for every operation all addressing modes are applicable. On following this type of regularity, the compiler's code generation will be simpler and much less complex it need not choose between two different passes for an instruction. One evidence of irregularity is when a specific operation demands for only specific registers. For example, in case of taking D = (A + B) \*C in which the addition operation need not have to look out for an even register and on register allocation it may end up with an even or odd one but the multiplication process which chooses an even register will have to make an extra data to move to compute the expression. This would result in having available registers but not the one needed (in this case even register) for register specific applications.

**Provide primitives, not solutions**—the generalization of a high level language functionality often fails results in supporting one high level language well and creating a semantic clash in the other languages. So it is much better not to add the special features in the instruction sets so that the features in the architecture are much generalized for use of all languages and can be synthesizing its own necessary solution from the given set of instruction sets.

Simplify trade-offs among alternatives—the biggest challenge for current compilers is dealing with a large case analysis. When several suggestions are made for a specific statement the compiler can choose the simple instruction set and implement the goal of the statement but the decision making time itself is more to choose which is the best and efficient instruction set of those available which consumes most of the compilation time. With pipelining and cache memory too it is difficult to handle the code size that is generated after compilation which was comparatively much less earlier. It is more important for the compiler writer to understand the alternative code sequences suggested and then choosing the best instruction set for the statement. The register-memory architecture is the most difficult tradeoff in deciding how many times a variable should be referenced before it is cheaper to load it into a register. This threshold point is very hard to compute and, in fact, may vary among models of the same architecture.

The architecture provides instructions that bind the quantity known at compile time as constants. Not all variables that have a value at the compiler time can act the same way in run-time, and this case when considered vice-versa by the architecture makes the compiler writer's job more complex. Good counter examples of this principle include instructions that interpret values that were fixed at compile time. For instance, the VAX procedure call instruction (calls) dynamically interprets a mask saying what registers to save on a call, but the mask is fixed at compile time.

## **CONCLUSION**

An effective compiler allows a more efficient execution of application programs for a given computer architecture, while wellconceived architectural feature can support more effective, compiler optimization techniques. Both the compiler writer and machine designer have multiple objectives. When the compiler writer and the machine designer work on their objectives also having in mind the objectives of the other then it is possible achieve what they need to accomplish and also what can be accomplished using the feature or optimization built by them. The compiler writer will benefit by having more space to research on the optimization techniques of the compiler and the machine designer will profit on the reduced execution time it takes to implement because of the well structured architecture that complies with the needs of a compiler writer and also achieves its primary goals. From embedded micro-controllers to largescale multiprocessor systems, it is important to understand the interaction between compilers and computer architectures. A machine designer should upgrade his architecture in a way that helps implement the high-level languages. But the upgradation must take into consideration cost, reliability, and customer acceptance factors also. It is of no use if it is very high level language oriented as it fails to generalize the concept of how the same is dealt in other languages. Similarly, a compiler writer should apply the semantics that are provided in the source code and translate the same to the code that can be interpreted by the machine for hardware implementation and also provide a user-friendly interface that doesn't make the work of the program complex. Correctness and efficiency is the major factors that are expected from an efficient compiler. To achieve both it needs a proper interaction with the computer architecture and an understanding of how things need to be conceived which would result in efficient and accurate compilers.

#### **REFERENCES:**

- [1] William A. Wulf, "Compilers and Computer Architecture", IEEE 0018-9162

- [2] John Hennessey and David Patterson, Computer Architecture A Quantitative Approach (fifth edition)

- [3] Torben Egidius Mogense, Basics of Compiler Design

- [4] Donavan, John J. Systems Programming. New York, Düsseldorf: McGraw-Hill, 1972. Print.

- [5] Lee, Gyungho, and Pen-Chung Yew. Interaction between Compilers and Computer Architectures. Boston: Kluwer Academic, 2001. Print.

- [6] <u>http://ocw.mit.edu/courses/electrical-engineering-and-computer-science/6-</u>035-computer-language-engineering-sma-5502-fall-2005/lecture-notes/14 wrapup.pdf

- [7] Kurt Keutzer, Wayne Wolf Anatomy of a Hardware Compiler AT&T Bell Laboratories Murray Hill NJ, 1988 ACM O-8979 l-269-1/88/0006/0095.

- [8] Mano, M. Morris. Computer Systems Architecture. Rockville, Mar.: Computer Science, 1982. Print.

- [9] Hamacher, V. Carl., Zvonko G. Vranesic, and Safwat G. Zaky. Computer Organization. New York: McGraw-Hill, 1984. Print.

- [10]http://en.wikipedia.org/wiki/Optimizing\_compiler#Specific\_techniques.

- [11] https://www.inkling.com/read/computer-architecture-hennessy-5th/appendix-a/section-a-8

- [12] http://www.tkt.cs.tut.fi/tools/public/tutorials/synopsys/design\_compiler/gsdc.html#arch\_opt