RESEARCH ARTICLE OPEN ACCESS

# HIGH THROUGHPUT POLAR CODES OF LIST DECODER ARCHITECTURE

## <sup>1</sup>RAJESH KANUGANTI, <sup>2</sup>SABAVATH KINZY BAI

1M-Tech, Dept. of ECE,Khammam Institute of Technology and Sciences,Khammam 2Assoc. Prof,Dept. of ECE,Khammam Institute of Technology and Sciences,Khammam

## **Abstract:**

Meanwhile, as obstacle discretionary twofold facts memory much fewer channels even as decoded through approach for using a low multifaceted nature dynamic cancelation (SC) calculation, the foul-up execution of the SC figuring is negative for polar codes with constrained piece lengths. The cyclic repetition check (CRC)- reinforced SC posting (SCL) unraveling figuring has needed blunder execution over the SC estimation. Although, modern CRC-helped SCL decoders cost the sick outcomes of lengthy unraveling idleness and obliged throughput. In this paper, a lessened torpidity list interpreting (RLLD) figuring for polar codes is proposed. Our RLLD estimation plays out the short assessment interpreting on a twofold tree, whose leaves look at to the bits of a polar code. In gift SCL decoding assessments, every ultimate one of the center focuses on the tree are investigated, and each and every doable end result of the information bits are taken into consideration. Or, however, perhaps, our RLLD estimation visits numerous a lousy package less focuses on the tree and considers abundance considerably less feasible eventual outcomes of the substances bits. At the thing whilst dealt with because it ought to be, our RLLD tally basically lessens the translating lethargy and, thusly, enhances throughput, whilst presenting little execution defilement. In the context of our RLLD consist of, we like manner suggest an excessive throughput posting decoder planning, that is trashy for ways reaching square lengths due to its adaptable incomplete mixture figuring unit. Our decoder building has been completed for distinctive square lengths and synopsis sizes the usage of the TSMC ninety-nm CMOS advancement. The utilization happens exhibit that our decoders fulfill simple nation of no recreation motion diminishing and move sufficiency trade separated and the alternative once-over polar decoders within the synthesis.

Keywords — gear utilizes, listing interpreting, low-lethargy, imaginative loosening up.

#### 1. INTRODUCTION

Polar codes are a vital jump ahead in the coding hypothesis, for the reason that they are able to accomplish the channel restriction of binary input symmetric memoryless channels and self-assertive discrete memoryless channels. Polar codes of rectangular duration N can be productively decoded by way of an

innovative cancelation (SC) calculation with an unpredictability of  $O(N \log N)$ . While polar codes of large piece duration (N > 220) method the limit of hidden channels under the SC calculation, for short or direct polar codes, the error execution of the SC calculation is greater horrible than rapid or LDPC codes. Bunches of endeavors have

simply been dedicated to the alternate of blunder execution of polar codes with brief or direct lengths. An SC listing (SCL) unraveling calculation performs advanced to the SC calculation. In, the cyclic repetition take a look at (CRC) is utilized to choose the yield codeword from L competition, wherein L is the rundown degree. The CRCsupported SCL (CA-SCL) translating calculation plays an awful lot superior to the SCL unraveling calculation to the detriment of immaterial misfortune in code charge. Regardless of its basically superior mistake execution, the system usage of SC primarily based rundown decoders nevertheless enjoy the unwell effects of lengthy unraveling idleness and restrained throughput because of the serial deciphering plan. So as to decrease the interpreting inertness of an SCbased rundown decoder, (M > 1) bits are decoded in parallel in, in which the decoding speed can be better through M times in an ideal global. Be that as it can, for the gadget executions of the calculations in, the real unraveling speed trade isn't always as a lot as M instances due to additional decoding cycles on locating the L most reliable approaches among 2ML applicants, wherein L is listing estimate. A product flexible SSC-list-CRC decoder turned into proposed in. For a (2048, 1723) polar+CRC-32 code,

the SSC-listing-CRC decoder with L=32 became seemed to be around 7 times faster than an SC-based rundown decoder. Be that as it could, it is indistinct whether or not the rundown decoder it is appropriate for gadget usage.

## 2.RELEGATED WORK

## 2.1Existing System

Notwithstanding its fundamentally more advantageous blunder execution. the equipment utilization of SC-based totally rundown decoders nonetheless experience the unwell results of lengthy unraveling idleness and confined throughput because of the serial translating plan. With a particular cease purpose to lessen the deciphering inertness of an SC-based totally rundown decoder, (M > 1) bits are decoded in parallel in, in which the disentangling charge may be stronger via M instances in a perfect world. In any case, for the device usage of the calculations in, the genuine disentangling pace trade isn't as lots as M times because of extra translating cycles on locating the L most stable ways amongst 2M L hopefuls, in which L is the rundown degree. A product flexible streamlined SC (SSC)- list-CRC decoder becomes proposed in. For a (2048, 1723) polar + CRC-32 code, the SSClisting-CRC decoder with L = 32 was appeared to be around seven times quicker than an SC-primarily based rundown

decoder. Be that as it may, it's far hazy whether the rundown decoder in is suitable for system execution.

## 2.2Proposed System

In this paper, an RLLD calculation is proposed to decrease the decoding idleness of SC list disentangling for polar codes. For a hub v, let Iv imply the aggregate number of leaf hubs which are related to facts bits. Give Xth a danger to be a predefined aspect esteem and X0 and X1 be predefined parameters. Additionally, our RLLD calculation chips away at a pruned tree. Subsequently, our RLLD calculation visits fewer hubs than the SCL calculation. The full parallel tree is pruned in stages.

1)Step 1: Starting from the complete tree portrayal of a polar code, mark all FP hubs to such a quantity that the determine hub of each of them is not an FP hub. For each marked FP hub, expel all its child hubs.

2)Step 2: Based at the pruned tree from Step 1, name all fee-zero and charge-1 hubs to such a quantity that the determine hub of each of those rate-zero and price-1 hubs isn't a charge-zero and charge-1 hub, one by one. In the subsequent, expel all youngster hubs of every of a named price-0 and rate-1 hub.

#### 3.IMPLEMENTATION

ISSN: 2395-1303

## 3.1 SCL Decoding on A Tree:

Like the SSC decoding calculation, we likewise play out the SC construct listing disentangling calculations in mild of a complete twofold tree Gn. The SCL disentangling is begun by sending the were given channel LLR vector to the root hub of Gn. As regarded in Fig. Three, without dropping all inclusive assertion, each interior hub v in Gn is actuated by means of getting L LLR vectors, av,0, av,1, •, αν,L-1, from its discern hub vice president and is in the rate of handing over L constituent codewords, βv,0, βv,1, • , βv,L-1, in which αv,l, and βv,l compare to interpreting way 1 for 1 = 0, 1, L - 1. Assume the layer listing of hub v ist,  $\alpha v$ , l and βv,l have 2 n-t LLR messages and twofold bits, one at a time, for l = zero, 1, L **-** 1.

## 3.2 Proposed RLLD algorithm:

In this paper, a lessened inertness listing unraveling (RLLD) calculation is proposed to lower the deciphering inactivity of SC listing translating for polar codes. For a hub v, let Iv suggest the aggregate range of leaf hubs which can be related to statistics bits. Give Xth a chance to be a predefined side esteem and X0 and X1 be predefined parameters. Our RLLD calculation performs out the SC construct list interpreting with appreciate to Gn and takes after the hub

actuation plan for Section III-An, apart from when the sure form of hubs are enacted. These hubs parent and repair the codewords to their determine hubs at the same time as refreshing the unraveling methods and their measurements, without actuating their tyke hubs.

#### **3.3 Parameters of Our RLLD Algorithm:**

For our RLLD calculation, the back codewords from charge-1 hubs with Iv>Xth are gotten with the aid of selecting tough alternatives at the got LLR vectors. The different fee-1 hubs are prepared via our CG calculation. Note that each the tough preference technique and our CG calculation may want to cause capacity mistake execution debasement given that in a super world we must recollect 2 Iv competitor codewords for each decoding way. With greater price-1 hubs (diminishing Xth) being prepared by using the difficult desire approach, the unraveling dormancy may be decreased at the value of extra mistake execution debasement. Moreover, keeping in mind the end aim to spare calculations, manner measurements live unaltered whilst a rate-0 hub is actuated, which may additionally cause blunder execution corruption. The decisions of X0 and X1 are tradeoffs among execution intricacy and completed deciphering inertness

diminishment. In an excellent world, we need X0 and X1 to be as extensive as doable with the goal that greater statistics bits could be decoded in parallel. Since the number of adders required through Alg. 2 is corresponding to 2 X0X1, the estimations of X0 and X1 are constrained by means of system executions.

### 3.4 Comparison with Related Algorithms:

On the off hazard that we play out the SC based rundown translating calculations, on a tree, at that factor each one of the 2N - 1hubs of the tree might be enacted. For our RLLD calculation, mean na as the quantity of actuated hubs. At that factor, we've got na < 2N - 1, where na is managed by using the piece duration N, the code price, the areas of solidified bits and the parameters X0 and X1. X0 and X1 are utilized to recognize all FP hubs. The lower of the quantity of initiated hubs will circulate into lessened disentangling inertness and elevated throughput. Take the (eight, three) polar code, count on X0 = 1 and X1 = 2, at that factor simply five (hubs 0, 1, 2, 5, and six) must be initiated with the aid of our RLLD calculation, though the calculations in need to enact every of the 15 hubs. The CA-SCL unraveling calculation was likewise executed on a paired tree in. low-inaction Contrasted and the list

interpreting calculation, our RLLD calculation utilizes the proposed MBS calculation to method FP hubs, at the same time as FP hubs were handled by using initiating its kid hubs in. Our MBS calculation brings approximately faded disentangling inertness at the value of capacity blunder execution misfortune.

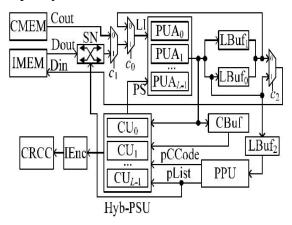

Fig 1 Architecture Diagram 4 RESULTS

### **4.1Experimental Results**

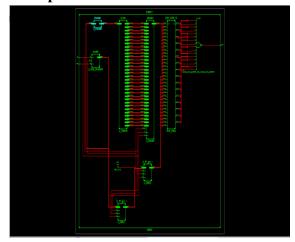

Fig 2:RTL Schematic:

ISSN: 2395-1303

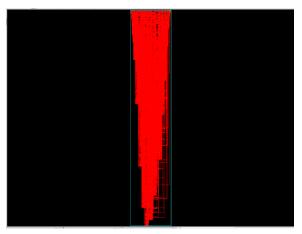

Fig 3: Technological Schematic:

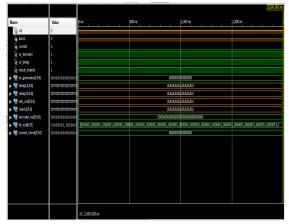

Fig 4: Simulation Output: 5.CONCLUSION

In this paper, an RLLD calculation is proposed for polar codes. The proposed list translating calculation brings about a high throughput listing decoder engineering for polar codes. A MEQ technique is also proposed to lessen the measure of message memories. The proposed listing decoder layout may be adjusted to expansive piece lengths because of our Hyb-PSU, which is territory effective. The execution aftereffects of our excessive throughput list decoder show noteworthy favorable circumstances

over contemporary pleasant in elegance SCL decoders.

#### **6.REFERENCE**

- [1] J. Lin, C. Xiong, and Z. Yan, "A reduced latency list decoding algorithmfor polar codes," in Proc. IEEE Workshop on Signal Processing Systems(SiPS), Belfast, UK, October 2014, pp. 56–61.

- [2] J. Lin and Z. Yan, "A hybrid partial sum computation unit architecture for list decoders of polar codes," in IEEE Int. Conference on Acoustics, Speech, and Signal Processing (ICASSP), 2015, [Online:http://arxiv.org/abs/1506.05896].

- [3] E. Arıkan, "Channel polarization: a method for constructing capacityachieving codes for symmetric binary-input memoryless channels," IEEE Trans. Info. Theory, vol. 55, no. 7, pp. 3051–3073, Jul. 2009.

- [4] E. Sasoglu, E. Teltar, and E. Arıkan, "Polariztion for arbitrary discretememoryless channels," in Proc. IEEE Int. Symp.on Information Theory, Seoul, South Korea, Jun. 2009, pp. 144–148.

- [5] C. Leroux, A. J. Raymond, G. Sarkis, and W. J. Gross, "A semi-parallel successive-cancellation decoder for polar codes," IEEE Trans. Signal Process., vol. 61, no. 2, pp. 289–299, Jan. 2013.

- [6] I. Tal and A. Vardy, "List decoding of polar codes," IEEE Trans. Info.Theory, 2015, [Online; DOI: 10.1109/TIT.2015.2410251].

- [7] K. Niu and K. Chen, "CRC-aided decoding of polar codes," IEEECommun.Lett., vol. 16, no. 10, pp. 1668–1671, Oct. 2012.

- [8] B. Li, H. Shen, and D. Tse, "An adaptive successive cancellation listdecoder for polar codes with cyclic redundancy check," IEEE Commun.Lett., vol. 16, no. 12, pp. 2044–2047, Dec. 2012.

- J. [9] A. Balatsoukas-Stimming, J. Raymond, W. Gross, A. and Burg, "Hardware architecture for list successive cancellation decoding of polarcodes," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 8, pp.609-613, Aug. 2014.

- [10] J. Lin and Z. Yan, "An efficient list decoder architecture for polar codes," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 2015, to appear.

#### **Authors Profiles**

RAJESH KANUGANTIAssoc. Prof, Khammam Institute of Technology and Sciences(KITS), Khammam. He received M.Tech in E.I.E from Andhra University, Visakhapatnam, AP, India. His research interests include Fuzzy logic system used in Signal processing and Embedded Systems Design, Optoelectronics in MEMS. He had published 04 International Journal & 06 National Conference. He received his B. Tech in Electronics and Communication Engineering from JNTU, Hyderabad, AP. He has 9 years' experience in teaching field.

SABAVATH KINZY BAI Pursuing MTech in VLSI SD branch in Khammam

Institute of Technology and

Sciences(KITS),Khammam,Mail:

kinzyjoy14@gmail.com