RESEARCH ARTICLE OPEN ACCESS

# Design of Full Adder in 180nm Technology Using TG and Adiabatic Logic

Baljinder Kaur M.Tech Scholar (ECE) Narinder Sharma HOD (ECE)

\*\*\*\*\*

# **Abstract:**

The main goal of this paper to produce new low power solutions for very large scale integration(VLSI). The main focus of this research on the power consumption, which is showing an ever-increasing growth with scaling down of the technologies. The full adder is the most important component of any digital system applications. To limit the power dissipation, this full adder is designed with adiabatic technique PFAL and it compare with partial adiabatic technique ECRL. These analysis have done on TANNER simulator V 7 technology. The power is reduced up to 70-80% as compared to other methods.

# Keywords - ECRL, TG, PFAL, Full Adder. Adiabatic Circuit

\*\*\*\*\*\*\*\*\*\*\*\*

#### 1. Introduction

The demand for low power circuits has encouraged the designers to explore the new methods to design the VLSI circuits. Then, designers move towards the energy recovery techniques such as adiabatic techniques. The main sources of power dissipation are static consumption, dynamic power consumption and short circuit power consumption. Majority of power is dissipated in pull up network of conventional CMOS network and remaining power is stored on node capacitor [1]. This stored charge is wasted in ground. But, it can be recycled back and used as power clock again. It is mention in thermodynamic process which is a reversible logic. The adiabatic logic is worked on this thermodynamic phenomenon and it can recover the partial or whole power from the load. In this paper, authors have designed the full adder using partial adiabatic logic methods. One is ECRL (Efficient Charge Recovery Logic) and other is PFAL(Positive FeedbackAdiabaticLogic).Both methodologies have own significance and authors have also compare their results with each other and PFAL has better calculation and results as compared to partial ECRL. It gives better performance in terms of energy consumption, useful frequency range and robustness against technology variation [2].

# 1.1 Transmission Gate Logic

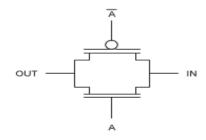

A transmission gate is constructed by combination of NMOS and PMOS transistors with complementary gate signals. It gives full output swing and its uses can increase the speed in CMOS circuits. There is no isolation between the input and output [3].

Fig 1: Transmission Gate Logic [3]

# 1.2 Adiabatic Principle

The word ADIABATIC emanates from a Greek word that is utilized to describe

thermodynamic processes that exchange no energy with the environment and therefore, no energy loss in the form of dissipated heat. In authentic-life computing, such ideal process cannot be achieved because of the presence of dissipative elements like resistances in a circuit. However, one can achieve very low energy dissipation by decelerating the speed of operation and only switching transistors under certain conditions. The signal energies stored in the circuit capacitances are recycled instead, of being dissipated as heat. The adiabatic logic is also known as ENERGY RECOVERY CMOS. In the adiabatic switching approach, the circuit energies are conserved rather than dissipated as heat. Depending on application and the system requirements, this approach can sometimes be used to reduce the power dissipation of the digital systems. Here, the load capacitance is charged by a constantcurrent source (instead of the constant-voltage source as in the conventional CMOS circuits). Here, R is the resistance of the PMOS constant charging network. Α corresponds to a linear voltage ramp [4].

Assume, the capacitor voltage  $V_c$  is zero initially.

P(t) in the switch =

$$I^2 R$$

1.2

Energy during charge =

$$(I^2 R)T$$

1.3

$$E = I^2 R = (CV|T)^2 RT = \frac{\sigma^2 v^2}{RT}$$

1.4

$$E = E \operatorname{diss} = \frac{RC}{T} CV^{2} = \frac{2RC}{T} \frac{1}{2} CV^{2}$$

1.5

where, the various terms of Equation (1.3) are described as follows:

E — energy dissipated during charging,

Q — charge being transferred to the load,

C — value of the load capacitance,

R — resistance of the MOS switch turned on,

V — final value of the voltage at the load,

T- time [5].

Now, a number of observations can be made based on Equation (1.3) as follows:

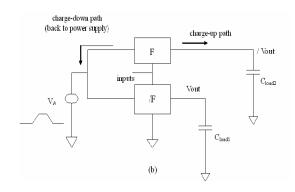

Fig 2: Adiabatic Logic [6]

- (i) The dissipated energy is smaller than for the conventional case, if the charging time T is larger than 2RC. That is, the dissipated energy can be made arbitrarily small by increasing the charging time,

- (ii) Also, the dissipated energy is proportional to R, as opposed to the conventional case, where the dissipation depends on the capacitance and the voltage swing. Thus, reducing the on-resistance of the PMOS network will reduce the energy dissipation [7].

#### 1.2.1. Types Of Adiabatic Logic:

- 1.2.1.1 Partially adiabatic logic. They are classified as:

- i) Efficient charge recovery logic (ECRL)

- ii) Quasi Adiabatic Logic (QAL)

- iii) Positive feedback adiabatic logic (PFAL)

- iv) 2N-2N2P Logic

- v) True single phase adiabatic logic (TSAL)

- 1.2.1.2 Fully adiabatic logic. They are classified as

- i) Pass transistor adiabatic logic

- ii) 2 Phase adiabatic Static CMOS logic (2PASCL)

- iii) Split rail charge recovery logic (SCRL) [8].

# 1.2.2. ECRL Logic

ECRL logic is that in which precharge and recovery phases are simultaneously worked and by this implementation, the power consumption is minimize up to greater extent. This method does not use the precharge diode and generates less energy dissipation. As

compared to other methods of energy recovery, it uses least number of PMOSFETS.It uses only two PMOSFETS for precharge and recovery phases. Due to this cross coupled PMOSFETS, the output is stored and it also charge and discharge the load capacitor according to the transition of the constant supply [9].

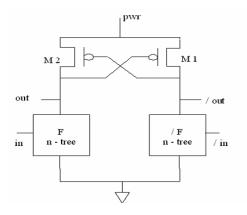

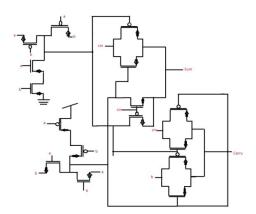

Fig 3: ECRL Logic Circuit [9]

The fig.3 shows two cross coupled PMOS transistors M1 and M 2 and two NMOS transistors logical blocks. In NMOS functional tree, one side is pull up network and other is pull down network. Both are the complement of each other. An AC ramp power supply is used in adiabatic as compared to DC power supply because it has good performance during energy precharge and recovery phases. The outputs out and out/ are drive the constant energy from power supply that is independent of input signal.ECRL always provides the full swing output. For instance, when the voltage approaches to threshold voltage then the PMOS transistors gets turned off automatically [10].

#### 1.2.3. PFAL Logic

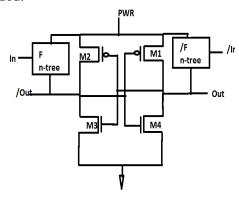

PFAL is partial energy recovery circuit and its core of all adiabatic circuit is made by adiabatic amplifier, a latch made up of 2 PMOSFETS M1- M2 and 2 NMOSFETS M3-

M4.Due to these MOS transistors ,the logic level degradation on the outputs nodes can be avoided.

Fig 4: PFAL Logic Circuit [11]

The functional blocks of PFAL are in parallel with the PMOSFETS of adiabatic amplifier and create a transmission gate process. The two F trees realize the logic functions. It is also generates the positive and negative outputs swing [11].

# 2. LOGIC DESIGN STYLES

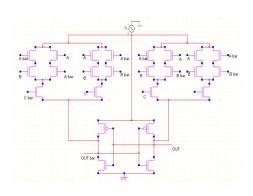

#### 2.1 Full Adder circuit using TG

A basic full adder circuit consists of three inputs A, B, C and two outputs sum and carry. Transmission gate logic based full adder is designed with PMOS and NMOS combination and they placed opposite to each other. It is the simplest and easiest method but it dissipated more heat during transition. [12].

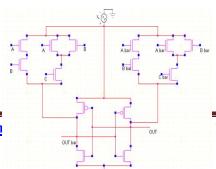

Fig 5: Full Adder circuit using TG [12]

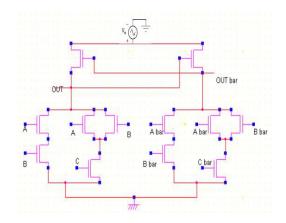

### 2.2 Full Adder Circuit Using ECRL Logic

ECRL stands for efficient charge recovery logic. It is also known as cascade voltage switch logic with differential logic. The logic in the functional block can be realized with NMOSFETS only. The NMOSFET section is fabricated in pull down function. During precharge phase, the pull up network does work and pull down network does not conduct. Outputs hold the valid logic levels and this condition is maintained during hold phase. When the discharge or recovery phase conducts then the sum/ returns its whole power to the supply voltage. In other words, clock is work as power clock and power supply [13]. The sum and carry equations are given below.

$$S = \overline{A} \overline{B} C + \overline{A} \overline{B} \overline{C} + A \overline{B} \overline{C} + A \overline{B} C + A \overline{B} C$$

$$C = \overline{A} \overline{B} C + A \overline{B} C + A \overline{B} C + A \overline{B} C$$

Fig 6: ECRL Sum Circuit

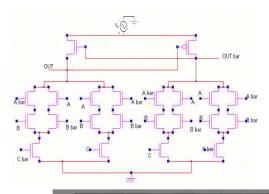

Circuit Using PFAL Logic

**Full** Adder

PFAL is same as transmission gate logic. But, the major difference between them is that the PFAL latch can minimize the coupling effects and in construction, its latch is made up of two NMOSFETS and two PMOSFETS. The sum and carry equations are implemented on this basis and it produces two outputs separately.Sum,Sum bar, Carry and Carry bar are the four outputs of this circuit[13].

Fig 8: PFAL Sum Circuit

Fig 9: PFAL Carry Circuit

#### 3. SIMULATED WAVEFORMS

In this paper, different methodologies are used to design the full adder using transmission gate logic and adiabatic logics. The full adder is designed on the s-edit of PSPICE software of tanner version 7. The simulation results of both the logics are presented in this section.

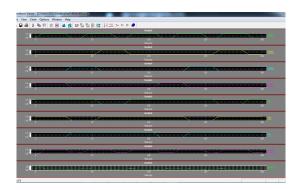

Fig 10: Simulation results Of Full Adder Using TG Logic

Figure 10 indicates that the simulated waveforms of full adder using TG. The bottom line indicate output signal and top four are inputs.

Fig 11: Simulation results Of Full Adder Sum Using ECRL Logic

Figure 11 indicates that the simulated waveforms of full adder sum using ECRL. The bottom two lines indicate output signal and top sevens are inputs.

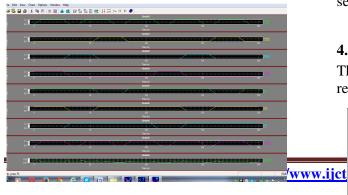

Fig 12: Simulation results Of Full Adder Carry Using ECRL Logic

Figure 12 indicates that the simulated waveforms of full adder carry using ECRL. The bottom two lines indicate output signal and top sevens are inputs.

Fig 12: Simulation results Of Full Adder Sum Using PFAL Logic

Figure 12 indicates that the simulated waveforms of full adder sum using PFAL.The

bottom two lines indicate output signal and top sevens are inputs.

Fig 13: Simulation results Of Full Adder Carry Using PFAL Logic

Figure 13 indicates that the simulated waveforms of full adder sum using PFAL. The bottom two lines indicate output signal and top sevens are inputs.

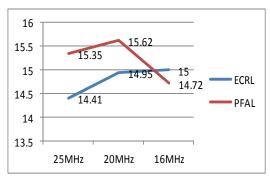

#### 4. RESULTS & COMPARISON

This section demonstrates the comparison results of conventional CMOS and adiabatic

| Frequen<br>cy | Full<br>Adder<br>(ECRL) | Full<br>Adder<br>(PFAL) | logic<br>in<br>terms |

|---------------|-------------------------|-------------------------|----------------------|

| 16MHz         | 15µw                    | 14.72μw                 | of                   |

| 20MHz         | 14.95µw                 | 15.26μw                 | avera                |

| 25MHz         | 14.41µw                 | 15.35µw                 | ge<br>powe           |

r consumption, delay and frequency. The two graphs shows the comparison of frequency with delay and power consumption and the

other shows the results of maximum frequency and transistor count.

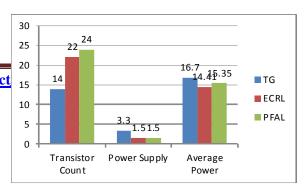

Fig 14: Graph For Transistor Count, Power Supply and Average Power for Full Adder between TG and Adiabatic logic

Fig 15:Avg. power verses Frequency For Full Adder

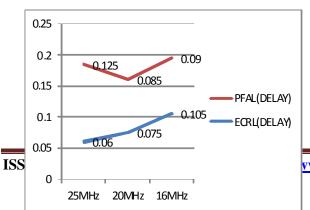

Fig 16: Delay verses Frequency For Full Adder

# "Table1: Power dissipation results for full adder with frequency"

"Table1" shows the power consumption analysis of adiabatic circuit ECRL and PFAL.The final results demonstrate that the energy dissipation of energy recovery logic ECRL is less as compared to PFAL logic.

"Table2: Average power dissipated, Power Supply and transistor count of full adder circuit using ECRL family and PFAL family"

"Table 2"shows the comparison analysis of various parameters such as transistor count, power supply and average power dissipated of full adder.

| Parameters          | Full<br>Adder<br>(TG) | Full Adder<br>(ECRL) | Full Adder<br>(PFAL) |

|---------------------|-----------------------|----------------------|----------------------|

| Transistor<br>Count | 14                    | 22                   | 24                   |

| Power<br>Supply     | 3.3V                  | 1.5V                 | 1.5V                 |

| Average power       | 16.7µw                | 14.41µw              | 15.35 μw             |

# $\hbox{``Table 3: Delay verses frequency analysis for full adder}\\$

"Table 3" shows the delay of the full adder with the different frequencies.

<u>vw.ijctjournal.org</u>

**Page 169**

| Frequen<br>cy | Full<br>Adder<br>(ECRL) | Full<br>Adder<br>(PFAL) |

|---------------|-------------------------|-------------------------|

| 16MHz         | 0.105s                  | 0.125s                  |

| 20MHz         | 0.075s                  | 0.085s                  |

| 25MHz         | 0.06s                   | 0.09s                   |

Technol ogy", Internati onal Journal Of Comput er Trends And

Technology,pp:800-804,April-2013.

- [8] B.Yasoda, S.Kallem Basha, "Performance Analysis Of Energy Efficient And Charge Recovery Adiabatic Techniques For Low Power Design", IOSR Journal Of Engineering (IOSRJEN), pp:14-21, Volume 3, June. 2013.

- [9] Sanjay Kumar 2009. Design Of Low Power CMOS Cell Structures Based On Adiabatic Switching Principle. M.techThesis.RegistrationNo.650861001, Thapar

- [10] Y. Moon and D. K. Jeong, "An Efficient Charge Recovery Logic Circuit," IEEE JSSC, Vol.31, No. 04, pp. 514-522, April 1996.

- [11] Premchand D.R, Siddlingamma, "Power Analysis of CMOS and Adiabatic Logic Design", Proceeding Of 07<sup>th</sup> IRF International Conference, Bengaluru, pp: 5-9,22<sup>nd</sup>June-2014.

- [12] Sansar Chand Sankhyan "Comparative Study Of Different Types of Full Adder Circuits", International Journal Of Engineering Research and Applications, Volume 3, pp: 1062-1064, Sep-Oct 2013.

- [13] B.Dilli Kumar, M.Barathi, "Design of Energy Efficient Arithmetic Circuits Using Charge Recovery Adiabatic Logic", International Journal of Engineering Trends and Technology, pp. 32-40, Volume 4-2013.

#### 5. Conclusion

Authors have designed the full adder circuit with efficient charge recovery logic and conventional CMOS.A power consumption is reduced up to 14.41µw as compared to transmission gate with 16.7µw and PFAL with power consumption. All 15.35µw parameters are simulated with tannerV7 on sedit at 180nm technology. The adiabatic logic operated with pulsed power supplies of 1.5V which is very less as compared to 3.3V used in TG.All results are verified at different frequencies and temperature. Due to these performance parameters, this approach is more convenient for energy efficient digital applications.

#### REFERENCES

- Richa Singh, Anjali Sharma, "Power Efficient Design Of Multiplexer Based Compressor Using Adiabatic Logic" International Journal Of Computer Applications, pp:45-50. November 2013.

- [2] Samik Samantha, "Study and Analysis Of Two Partially Adiabatic Inverters" International Conference On Communication, Circuits and Systems iC3S-2012, pp:17-19,2012.

- [3] Manisha, Archana, "A Comparative Study Of Full Adder Using Static CMOS Logic Style", International Journal Of Research In Engineering and Technology, Volume 3,pp:489-494, June-2014.

- [4] A.G.Dickinson and J.S.Denker, (1995), "Adiabatic Dynamic Logic," IEEE. Journal of Solid-static Circuits, pp 311-315, 1995.

- [5] Ashish Raghuwanshi,Prof. Preet Jain, "An Efficient Adiabatic CMOS Circuit Design Approach For Low Power Applications" International Journal Of Electronics Communication and Computer Engineering,pp:1400-1406, Volume 4, 2013.

- [6] Shewata Chawla, Ramanand Harijan, Harpal Singh, "Design Low Power 32-Bit Barrel Shifter using Efficient Charge Recovery Logic", International Journal Of Engineering and Advance Technology(IJEAT), Volume 2,pp:140-145,F

- [7] Nikunj R. Patel, Sarman K Hadia, "Adiabatic Logic For Low Power Application Using Design 180nm