# Study of Design Parameter Variations in Simple Grounded Active Inductor

Lakshmi V Nair, Prameela B

M.tech Student, ASIET kalady, vnair.025@gmail.com, 9847540039

Abstract— This paper presents a fundamental active inductor topology named Simple Grounded Active Inductor (SGAI) for analyzing variations in Q factor and inductance. Design parameters like aspect ratios and biasing of the transistors are varied and the Q factor and inductance variations are measured at 2.4GHz. The SGAI structure is simulated using Cadence Virtuoso spectre using 180nm technology and a supply voltage of 3.3 V. For a biasing current of  $500\mu A$  and aspect ratio of  $5\mu m/0.18\mu m$ , the Q factor is 2.45, inductance is 2.5nH, and the self resonating frequency is 23.47GHz at 2.4GHz. The designed SGAI circuit consumes a power of 3.3mW.

Keywords— SGAI, SRF, Q factor, SCAI, Regulated Cascode, CMOS, RFIC

#### INTRODUCTION

In order to make Moore's low pronouncing in radio frequency integrated circuits (RFIC), the RF components can no more be passive in nature. RFIC normally work between 300MHZ to 30GHZ. High Q factor inductor is a major parameter that determines the reliability and efficiency of CMOS RF blocks. Usually inductors are realized on chip as spiral inductors. But they consume a higher area and also has a limited Q factor due to various losses. The inductance and q factor of spiral inductors is determined by design parameters like total length, width, thickness of wire, number of loops, conductivity of the metal etc. Even though passive inductors are simpler to design, they possess a low Q factors in the range of 5 for bulk CMOS and 20 for SOI at GHz frequencies [1].

As the RFIC performance is mainly determined by the tank circuit, a reliable inductor design is inevitable. Active inductors are a promising solution in this scenario. They offer many advantages over their passive counter parts like small chip area, tunable inductance, high Q factor etc [2]. Even though there are several active inductor topologies in the literature most of them are based on gyrator-C configuration [3]. An ideal gyrator is a linear two port network that neither stores nor dissipates energy.

## **BASIC ACTIVE INDUCTORS**

Usually active inductors are build on gyrator type configuration where two transistors are connected in a back to back fashion [5]. The topology utilizes the parasitic capacitance of the transistors in order to make the overall circuit to behave inductive. Simple Grounded Active Inductor (SGAI) is the fundamental topology that uses two transistors to mimic the inductive behavior [10]. However the Q factor that can be achieved is limited and for improving the same, Simple Cascoded Active Inductors (SCAI) can be used. Problem with SCAI is the reduction in the frequency range of the operation. To alleviate that drawback, regulated cascode active inductors [6] are there which provide a better performance compared to SGAI in terms of Q factor and SCAI in terms of frequency range.

### A. Theory of operation of SGAI

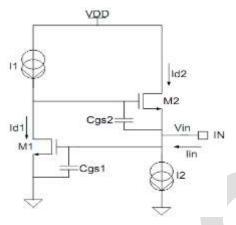

Input voltage  $V_{in}$  is applied to the gate of  $M_1$  which converts the voltage into a current that charges  $C_{gs2}$ . The voltage across  $C_{gs2}$  is then translated into current by  $M_1$  that maintain  $I_2$  as a constant [5]. Initially,  $I_{d2}$ = $I_2$ . Increasing  $I_{in}$  causes voltage across  $C_{gs1}$  to increase. This increases  $I_{d1}$  and since  $I_1$  is a constant current source, charges from  $C_{gs2}$  is extracted out to meet the increased current demand of  $M_1$ . Reduction in gate voltage along with increase in source voltage of  $M_2$  reduces  $I_{d2}$ . Now to hold KCL, the increase in input current is utilized by  $I_2$  to remain constant. In this manner SGAI resist the changes in current thereby mimicking inductive behavior.

Fig1: Circuit Schematic of SGAI illustrating parasitic capacitances.

#### B. Figure of merits of inductors

### Frequency range

A gyrator-C based active inductor exhibits inductive characteristics over a specific frequency range[8]. Lowest frequency bound is determined by the zero  $(\omega_z)$  and upper bound by the pole  $(\omega_o)$  of impedance transfer function. Gyrator-C network will be resistive when  $\omega < \omega_z$ , inductive when  $\omega_z < \omega < \omega_o$  and capacitive when  $\omega > \omega_o$ .  $\omega_o$  is also referred to as Self Resonating Frequency (SRF) [4] where the magnitude of impedance is at its peak.

### Q factor

The Quality factor or Q factor is a performance indicator that indicates the energy losses within a resonant element. It is dimensionless frequency dependent parameter and can be defined as the ratio of inductive reactance to resistance.

### **Inductance Tunability**

Inductance value can be tuned by varying the transconductance and biasing currents [11]. Since aspect ratio of inductor cannot be tuned once it is fabricated, it is done with biasing currents. So active inductors are beneficial in reconfigurable systems [1].

# Chip Area

Active inductors being implemented with active devices, reduces the chip area to a greater extend when compared with their passive versions.

### Linearity

Linearity defines the ability of active inductor to sustain a constant inductance and Q factor over a wide input power range [1]. Square law relationship followed by gate source voltage and drain current is the reason for nonlinearity in active inductors [11].

#### Noise

Active inductors exhibit a higher noise level compared to their passive counterparts [1]. The dominant contributors of noise are thermal noise in the transistor channel and flicker noise due to dangling bonds near the surface [12].

# C. Design considerations in SGAI

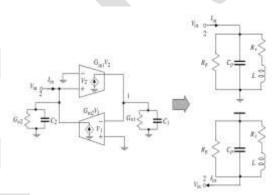

When the transconductors used for the synthesis of AI has finite input and output impedance, there will be parasitic capacitive (parallel capacitance  $C_p$ ) and resistive effects (parallel resistance  $R_p$  & series resistance  $R_s$ ) which make the structure lossy. Fig2 below shows the equivalent structure of AI with parasitic effects. Applying KCL at nodes 1 and 2 gives

Node1 =>

$$(sC_1 + G_{o1})V_1 - g_{m1}V_2 = 0$$

(1)

Node2 =>

$$-I_{in} + (sC_2 + G_{o2})V_2 - g_{m2}(-V_1) = 0$$

(2)

Admittance looking into node 2 is given by

$$Y = \frac{\sin}{v_2} = sC_2 + G_{o2} + \frac{1}{s(\frac{C_1}{gm_1gm_2}) + \frac{Go_1}{gm_1gm_2}}$$

(3)

Above equation can be represented by an equivalent RLC network (Fig2) with following parameters.

$$R_{p} = \frac{1}{Go2} \tag{4}$$

$$C_p = C_2 \tag{5}$$

$$R_{s} = \frac{Go1}{gm1gm2} \tag{6}$$

$$L = \frac{C1}{Gm1Gm2} \tag{7}$$

Fig2: Lossy single-ended gyrator-C active inductors.  $C_1$  and  $G_{o1}$ ,  $C_2$  and  $G_{o2}$  denote the total capacitance and conductance at nodes 1 and 2, respectively.

Theoretical equations relating figure of merits and design parameters of active inductors are [7][9]:

$$L = \frac{cgs2}{(gm1gm2)}$$

(8)

$$Q = \sqrt{\frac{\text{gm2cgs1}}{\text{gm1cgs2}}} \tag{9}$$

236 <u>www.ijergs.org</u>

$$Q = \frac{im\{Z\}}{re\{Z\}} \tag{10}$$

$$Q = \frac{wL}{Rs}$$

(11)

$$R_s = \frac{\text{Go1}}{\text{gm1gm2}} \tag{12}$$

## **DESIGN METHODOLOGY**

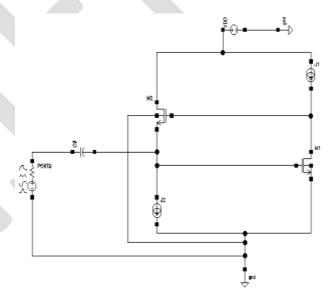

In this section, we discuss the design considerations and simulation results of SGAI. As many of the wireless communication techniques are operating in 2.4GHz, it is kept as the frequency of concern and L & Q factor are measured and optimized for 2.4GHz. For this frequency Q factor and inductance are measured by varying aspect ratios and biasing and dependency pattern in theoretical and practical cases are compared. For measuring SRF the design parameters are set meeting the following criteria.

TABLE I SGAI DESIGN REQUIREMENTS

| Technology      | 180nm  |

|-----------------|--------|

| V <sub>DD</sub> | 3.3V   |

| Frequency       | 2.4GHz |

| Q factor        | 2-3    |

| Inductance      | 2-3nH  |

.Fig3: Experimental setup of SGAI

#### A. Varying the aspect ratios

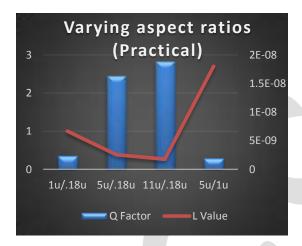

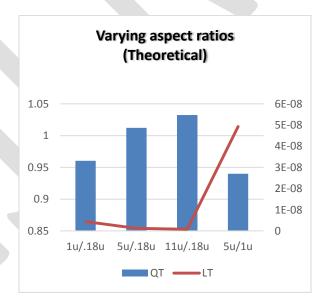

To understand the variations in Q factor and inductance with respect to aspect ratios, biasing currents  $J_1$  and  $J_2$  are arbitrarily fixed and aspect ratios of both transistors are varied in equal fashion.

Fig4: Q factor & L for varying aspect ratios- practical case

From the above figure, it can be concluded that increasing the aspect ratios of transistors increases the Q factor and reduces the inductance. As width of  $M_1$  & $M_2$  increases for a fixed length,  $g_{m1}$  and  $g_{m2}$  increases. Since L is inversely proportional to both  $g_{m1}$  and  $g_{m2}$  (eq.8), increasing width reduces L. Increase in  $g_{m1}$  and  $g_{m2}$  reduces effective series resistance Rs due to inverse proportionality (eq.12). Q factor which is inversely related to  $R_s$  thus increases for increasing width (eq.11). From the two graphs that have been plotted it is found that both L and Q factor follows the same pattern theoretically and practically. Variations in the values of theoretical and practical cases are due to the frequency of operation. Theoretical values are measured under its dc operating point and practical values are measured under the required operating conditions. So it can be concluded that both Q factor and L of the SGAI follows the basic relationships as defined in theory and practical values are used for verifying the design.

Fig5: Q factor & L for varying aspect ratios- theoretical case

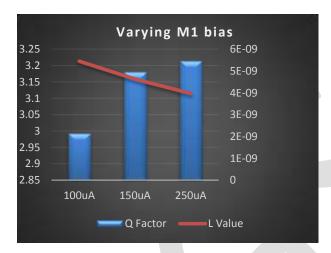

#### B. Varying biasing currents

Increase in  $J_2$  increase transconductance of  $M_1$  thereby improving Q factor and reducing L. As  $J_1$  is the bias for  $M_2$ , increase in  $J_1$  increases transconductance of  $M_2$  and since there is no change in aspect ratio of the transistor,  $c_{gs2}$  remains almost constant. Also  $g_{m2}$  and  $c_{gs1}$  are almost constants. Thus increasing  $J_1$  enhances Q factor and degrades L.

Fig6: Q factor & L for varying M<sub>1</sub> bias

Fig7: Q factor & L for varying M<sub>2</sub> bias

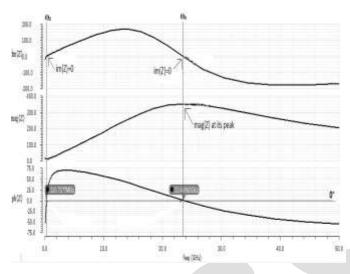

## C. Frequency range and power consumption

From the analysis carried out, parameters are fixed for obtaining an inductance of 2.5nH and Q factor in the range 2-3 for analyzing the frequency range and power consumption. Between  $\omega_z \& \omega_0$  ph{Z} is greater than 0° denoting an overall inductive nature. At SRF mag{Z} is at its peak, ph{Z} is zero (crossing from positive (inductive) to negative (capacitive)) and im{Z} becomes zero thereby making Q factor to be zero. The circuit draws a current of 1.003mA from power supply thereby consuming a power of 3.3mW.

Fig8: Inductive frequency range of SGAI

## TABLEII SGAI PERFORMANCE SUMMARY

| Technology       | 180nm     |

|------------------|-----------|

|                  |           |

| $V_{ m DD}$      | 3.3V      |

| Frequency        | 2.4GHz    |

|                  |           |

| Q factor         | 2.45      |

| L                | 2.5nH     |

| $\omega_{\rm z}$ | 310.73MHz |

| ωο               | 23.47GHz  |

| Power            | 3.3mW     |

# CONCLUSION

Through transistor level simulation, we have verified relationship between the design parameters and figure of merits of a basic active inductor topology named Simple Grounded Active Inductor both theoretically and practically. The structure is then optimized for an inductance of 2.5nH and Q factor of 2.45 for analyzing its inductive frequency range and power consumption. The analysis has shown a SRF of 23.47GHz which is around ten times the required frequency of operation.

#### **REFERENCES:**

- [1] Robert F, Cathelin P, Diet A, Villegas M, "A highly linear and tunable feed forward current source active inductor in 65nm CMOS technology for mobile applications" in Wireless and Microwave Technology Conference, 2011.

- [2] Chun-Lee Ler, Abu Khari Bin Aain, and Albert Victor Kordesch, "CMOS Active Inductor Linearity Improvement Using Feed-Forward Current Source Technique" in IEEE Transactions on Microwave Theory and Techniques, August 2009.

- [3] Murli U Nair, Yuanjin Zheng, Yong Lian, "An Active Inductor based Low-Power UWB LNA" in IEEE International Conference, September 2007.

- [4] Zito D, Pepe D, Fonte A, "High Frequency CMOS Active Inductor Design Methodology and Noise Analysis" in *IEEE Transactions on Very large Scale Integration Systems*, July 2014.

- [5] U Yodprasit and J Ngarmnil, "Q-Enhancing Technique for RF CMOS Active Inductor" in IEEE International Symposium on Circuits and Systems, May 2000.

- [6] William Bucossi and James P Becker, "Practical Considerations In The Use of CMOS Active Inductors" in IEEE Topical Meeting on Silicon Monolithic Integrated circuits in RF Systems, 2008.

- [7] Gao Zhiqiang, Xu Honglin, Zhang Zhongzhao, Lan Jinbao, "Design Consideration of Multi-band RF CMOS Filter Based on Active Inductors" *in IEEE Journal of Solid-State Circuits*, 2010.

- [8] Guochi Huang, Byung-Sung Kim, "Programmable Active Inductor Based Quadrature VCO Design" in Proceedings of Asia-Pacific Microwave Conference 2007

- [9] Hsieh-Hung Hsieh, Yu-Te Liao, Liang-Hung Lu, "A Compact Quadrature Hybrid MMIC Using CMOS Active Inductors" *In IEEE Transactions on Microwave Theory and Techniques*, vol. 55, NO. 6, June 2007

- [10] Sang-Ki Eun, Choon Sik Cho, Jae W. Lee, Jaeheung Kim, "A Low Power VCO Using Active Inductor For Low Phase Noise and Wide Tuning Range" in Proceedings of the 39th European Microwave Conference

- [11] Vincenzo Stornelli, Giorgio Leuzzi, Leonardo Pantoli, Stefano Del Re, "High Dynamic Range Bandpass Filters Design Based on Active Inductor" in Proceedings of the 6th European Microwave Integrated Circuits Conference

- [12] Mohsen Moezzi, M. Sharif Bakhtiar, "Wideband LNA Using Active Inductor With Multiple Feed-Forward Noise Reduction Paths" in IEEE Transactions on Microwave Theory and Techniques, vol. 60, NO. 4, April 2012