# Modelling and Simulation of Unipolar HVDC Link

Assistant Professor Karan Gupta<sup>1</sup>, Shubham Abrol<sup>2</sup>, Suvan Sharma<sup>3</sup>, Chahat Bakshi, Vikram Singh

Department of Electrical Engineering, GCET Jammu

Email address: \(^1\)karan74 \(\text{gupta@yahoo.com}\), \(^2\)sabrol538@gmail.com, \(^3\)suvansharma01@gmail.com

**Abstract**—The use of high voltage AC transmission of bulk power over long distance invite the attention of transmission of high voltage DC for long lengths of line. HVDC systems suffer relatively lower electrical losses and require relatively lower economic expenditure, for long distance transmission. In this paper we simulate a unipolar HVDC transmission link using twelve pulse thyristor convertors. The changes in output waveforms are noted for change in firing angles and DC fault conditions.

Keywords—HVDC, Unipoar, Rectifier, Inverter, Three Phase AC, Firing angle and DC fault.

# Introduction

Voltage conversion in an AC system is simple as high power levels and high insulation levels are allowed by an AC transformer in one unit, and also losses are low. Its simplicity and superiority of a three phase synchronous generator over DC generator led and encouraged the introduction of AC technology in the development of electrical power systems. But, disadvantages linking to AC transmission like limits on transmission capacity due to inductive and capacitive elements of overhead lines, impossibility of direct connection between two AC systems with different frequencies and system instability caused by direct connection between two AC systems with the same frequency compelled and engaged engineers over ages in substituting AC transmission by DC transmission. With the invention of mercury arc rectifiers in the 20<sup>th</sup> century, line commutated current sourced converter could be designed. Next major development occurred when thyristor valves replaced mercury arc valves. The need for parallel connection and large number of series connected thyristors per valve has been extinguished by the development of thyristors with high current and voltage rating. Innovations and appreciable development in areas of HVDC have increased reliability of HVDC systems significantly.

## METHODOLOGY

## General Overview

In this paper we have illustrated the modelling of a unipolar HVDC link using 12 pulse thyristor converters and perturbations are applied to examine performance of the transmission system. A 1000 MW (500kV, 2KA) DC unipolar link is used to transmit power from a 500kV, 5000 MVA, 50Hz system to a 345 kV, 10000 MVA, 50Hz system. The AC systems are represented by an emf source in series with inductance and damped L-R equivalents.

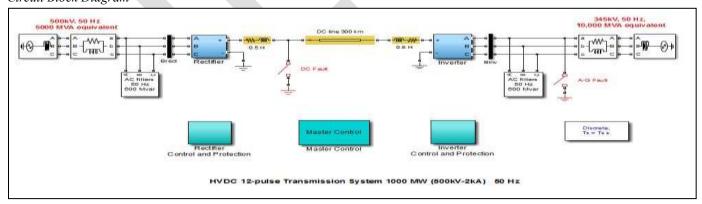

# Circuit Block Diagram

Fig. 1: Circuit Block Diagram

The rectifier and inverter are 12-pulse bridge converters using two Universal Bridge blocks. These two Universal Bridge blocks are connected in series. A 300 km line is used to interconnect the converters. 0.5H smoothing reactors are used on both sides. The Three Phase Three Winding blocks are used as the converter transformers blocks. These are Wye grounded on primary side, Wye connected on secondary side and Delta on tertiary side. The tap changing of the transformer is not simulated and hence the tap positions are fixed and determined by a multiplication factor of 0.9 for the rectifier and 0.96 for inverter which applied to the primary voltage of the three

312 <u>www.ijergs.org</u>

phase three winding transformers. The HVDC converter acts as a source of harmonic currents for the AC side. and harmonic voltages for the DC side. The order of the ac harmonic is one less than or greater than the intergral multiple of number of pulses and that of dc harmonic is integral multiple of number of pulses.

k being an integer and p being number of pulses,

Since we have used 12 pulse circuit, hence the harmonics on AC side are of the order 11,13,23,25 and so on and that on DC side is of order 24,36 and so on.

AC filters are used to control the spreading out of the odd harmonic currents on the AC system and high passes damped filters are used to control even harmonics. The filters are grouped into two subsystems. These filter subsystem also contains a capacitor bank which is used to provide reactive power compensation to the circuit. This reactive power compensation is required because of the different firing angle of the thyristors in the converter circuit. The series RLC filter is used to eliminate the 11<sup>th</sup> and 13<sup>th</sup> harmonic and high pass damped filter is used to eliminate 24<sup>th</sup> harmonic.

The breaker block applies faults on the reactifier DC side to check for the stability of the system during fault. The sample time of  $Ts=50\mu s$  with the disrete steps are used for both the HVDC system and the rectifier and inverter control and protection subsystems. These control susbsystems are basically the PI controllers which takes the error inputs and based on those inputs generate the output current reference for both the rectifier and inverter and helps in the starting and stopping of the HVDC power transmission. The protection systems can be switched ON and OFF.

#### SIMULATIONS

In the first case the circuit is run and output waveforms are analyzed. In second case the firing angle is changed and circuit is simulated. In the third and final case DC fault condition is simulated and output waveforms analyzed accordingly.

#### Case 1

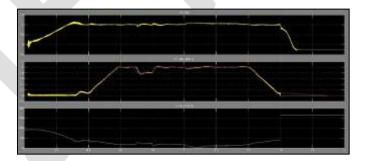

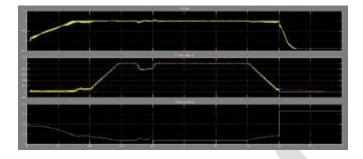

The simulation of unipolar HVDC link is run with the inverter firing angle between 92° and 166°. The simulation is started, current is first ramped up to the steady state, then negative current step is added, after some time positive voltage step is added and the current is ramped down at the time of stopping of the system. The different waveforms are studied in the rectifier and inverter scope. The waveforms reproduced are as follows:-

Fig. 2: V<sub>dL</sub>, I<sub>d</sub> and alpha\_order v/s time waveforms across Rectifier

Fig. 3: V<sub>dL</sub>, I<sub>d</sub> and alpha\_order v/s time waveforms across Inverter

At the start of simulation the converters pulse generators in the master control are deblocked and the power transmission started by ramping the reference current at t=20ms and triggering the 12 pulse rectifier and inverter circuit with firing angle of 92° and 102° respectively. At t=0.3s, the reference current reaches a value of 0.1pu, the DC current starts to build, the inverter firing angle  $\alpha$  reaches the maximum value of  $166^{\circ}$  and the voltage  $V_{dL}$  across rectifier and inverter crosses the reference voltage 1pu and makes an overshoot to 1.2pu meanwhile the current I<sub>d</sub> takes an overshoot and reaches the value around 0.1pu. At t=0.4s, the reference current is ramped from 0.1 to 1 pu (5kA) in 0.18s (5pu/s) and the dc current  $I_d$  increases with the reference current keeping  $V_{dL}$  constant and then the dc current shifts from transient to steady state at t=0.58s. The trace 1 of rectifier and inverter scope shows the DC line voltage (1pu=200 kV), trace 2 shows the reference current and the measured I<sub>d</sub> current (1pu=5 kA) and trace 3 shows the firing angle of both the rectifier and inverter. The rectifier and inverter are current and voltage controlled device resp. but during ramp both controls current. At t=0.7s, a -0.2pu step is applied during 0.1s to the reference current, hence the current I<sub>d</sub> decreases with the step but the slight decrease in voltage seen keeping it constant. At t=1.0s, a 0.1pu step is applied during 0.2s at the inverter reference voltage. The voltage takes the shoot to 1.1pu mean while current decreases to 0.9 and becomes constant after which voltage regulator regulates the voltage and the voltage and current reaches the value of 1pu. The firing angle  $\alpha$  of rectifier and inverter are around 16.5 degree and 143 degree respectively at t=1.35s. At t=1.4s the controller stops the simulation by ramping down the current to min value of 0.1pu keeping the voltage constant. At t=1.6s the firing angle alpha is forced to 166 deg at the rectifier and to 92 deg at the inverter which extinguishes the current and brings down the DC voltage due to the trapped charge in the line capacitance. At t=1.7s the pulses are blocked in both converters.

Fig. 4: AC voltage and current v/s time On Rectifier Side

Fig. 5: AC voltage and current v/s time On Inverter Side

At t=0 s,  $V_{abc\_r}$  is around 1.1 pu and  $V_{abc\_i}$  is around 1.06 pu but the  $I_{abc\_r}$  and the  $I_{abc\_i}$  are 0 pu/100 MVA. Then At t=0.3 s,  $I_{abc\_r}$  and  $I_{abc\_i}$  increases to 2 pu/100 MVA and 1.6 pu/100 MVA resp. meanwhile  $V_{abc\_r}$  and  $V_{abc\_i}$  decreases to 1.08 pu and 1.05pu resp. At t=0.4 s,  $V_{abc\_r}$  decreases from 1.08 pu to 0.9 pu and  $V_{abc\_i}$  decreases from 1.05 pu to 1 pu and the  $I_{abc\_i}$  increases from 1.5 pu/100 MVA to 12 pu/100 MVA and  $I_{abc\_i}$  increases from 1 pu/100 MVA to 11 pu/100 MVA. At t=0.7s,  $V_{abc\_r}$  and  $V_{abc\_i}$  increases to 1pu and  $I_{abc\_i}$  and  $I_{abc\_i}$  decreases to 9 pu/100 MVA and 8.2 pu/100 MVA. At t=0.8s,  $V_{abc\_r}$  and  $V_{abc\_i}$  continue to remain same and  $I_{abc\_i}$  increases to 12pu/100 MVA and 11.2pu/100MVA. At t=1.4s,  $V_{abc\_r}$  starts increasing to 1.1 pu but  $V_{abc\_i}$  is same and  $I_{abc\_i}$  drops from 12 to 1.1pu/100 MVA and 11 to 1 pu/100 MVA respectively. At t=1.6s,  $V_{abc\_r}$  and  $V_{abc\_r}$  are same and  $V_{abc\_r}$  and  $V_{abc\_i}$  increases are and  $V_{abc\_i}$  finally attains a value of 0.1pu/100 MVA.

#### Case 2

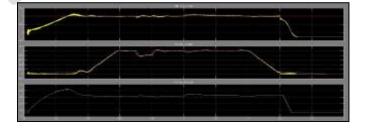

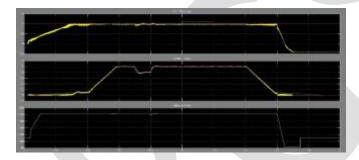

The simulation of unipolar HVDC link is run with the change in inverter firing angle between 105° and 142°. This is because whenever there is change in load in the inverter end (the load can be inductive, capacitive or anything), the required current changes or

the reactive power compensation is required hence the firing angle of the inverter is changed manually. The simulation is started, current is first ramped up to the steady state, then negative current step is added, after some time positive voltage step is added and the current is ramped down at the time of stopping of the system. The different waveforms are studied in the rectifier and inverter scope. The waveforms reproduced are as follows:-

Fig. 6:  $V_{dL}$ ,  $I_{d}$  and alpha\_order v/s time waveforms across Rectifier

Fig. 7: V<sub>dL</sub>, I<sub>d</sub> and alpha\_order v/s time waveforms across Inverter

At the start of simulation the converters pulse generators in the master control are deblocked and the power transmission started by ramping the reference current at t=20 ms and triggering the 12 pulse rectifier and inverter circuit with firing angle of 92° and 117°. At t=0.3 s, the reference current reaches a value of 0.1 pu, the DC current starts to build, the inverter firing angle α reaches the maximum value of 142° and the voltage V<sub>dL</sub> across rectifier and inverter takes an shoot to 1 pu and then reaches the steady state 1 pu value, meanwhile the current I<sub>d</sub> increases from 0 pu and reaches the value around 0.1 pu. At t=0.4s, the reference current is ramped from 0.1 to 1 pu (2 kA) in 0.18 s (5 pu/s) and the dc current  $I_d$  increases with the reference current keeping  $V_{dL}$  constant and then the DC current shifts from transient to steady state at t=0.58 s. The trace 1 of rectifier and inverter scope shows the DC line voltage (1 pu=200kV), trace 2 shows the reference current and the measured I<sub>d</sub> current (1pu=5kA) and trace 3 shows the firing angle of both the rectifier and inverter. The rectifier and inverter are current and voltage controlled device resp. but during ramp both controls current. At t=0.7s, a -0.2 pu step is applied during 0.1 s to the reference current, hence the current I<sub>d</sub> decreases with the step and the rectifier voltage decreases to 0.9 pu and then increases to 1.1 pu at the end of step but the slight decrease in inverter voltage seen keeping it constant. At t=1.0s, a 0.1 pu step is applied during 0.2 s at the inverter reference voltage. The voltage and current remains constant. The firing angle  $\alpha$  of rectifier and inverter are around 18.5 degrees and 142 degrees respectively at t=1.35s. At t=1.4s the controller stops the simulation by ramping down the current to min value of 0.1pu keeping the voltage constant. At t=1.6s the firing angle alpha is forced to 166 deg at the rectifier and to 92 deg at the inverter which extinguishes the current and brings down the DC voltage due to the trapped charge in the line capacitance. At t=1.7s the pulses are blocked in both converters.

Fig.8: AC voltage and current v/s time on Rectifier Side

315

Fig.9: AC voltage and current v/s time on Inverter Side

At t=0s,  $V_{abc\_r}$  and  $V_{abc\_i}$  are around 1.1pu and 1.06pu respectively but both the  $I_{abc\_r}$  and  $I_{abc\_i}$  are 0 pu/100 MVA. Then at t=0.3s,  $I_{abc\_r}$  and  $I_{abc\_i}$  increases to 1.5 pu/100 MVA and 1.3 pu/100 MVA respectively but  $V_{abc\_r}$  decreases to 1.08 pu keeping  $V_{abc\_i}$  constant. At t = 0.4 s,  $V_{abc\_r}$  and  $V_{abc\_i}$  decreases to 0.9 pu and 1.06pu but the  $I_{abc\_r}$  increases from 1.35 pu/100 MVA to 11.8 pu/100 MVA and  $I_{abc\_i}$  from 1.2 pu/100 MVA to 11.1 pu/100 MVA. At t=0.7s,  $V_{abc\_r}$  and  $V_{abc\_i}$  increases to 0.98 pu and 1.01pu but  $I_{abc\_r}$  and  $I_{abc\_i}$  decreases to 9.2 pu/100 MVA and 8.6 pu/100 MVA. At t=0.8s, both  $V_{abc\_r}$  and  $V_{abc\_i}$  continue to remain same and  $I_{abc\_r}$  increases to 12pu/100 MVA and  $I_{abc\_i}$  from 11.1 pu/100 MVA. At t=1.4s,  $V_{abc\_r}$  increases to 1.1 pu keeping  $V_{abc\_i}$  constant but  $I_{abc\_r}$  drops from 12 to 1.1pu/100 MVA and  $I_{abc\_i}$  from 11.1 to 1.5 pu/100 MVA. At t=1.6s, both  $V_{abc\_r}$  and  $V_{abc\_i}$  are same and both  $I_{abc\_r}$  finally attains a value of 0.05 pu/100 MVA.

### Case 3

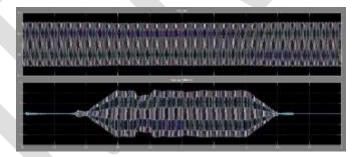

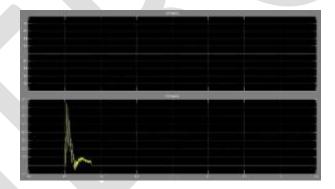

The simulation of unipolar HVDC link is run with inverter firing angle between 92° and 166° with the dc fault. The DC fault is mainly the line to ground fault of the DC line. DC fault is applied by deactivating the steps applied on the current reference and on the voltage reference in the Master Control and in the Inverter Control and Protection respectively by setting the switches in lower position. The simulation is started, current is first ramped up to the steady state, then the dc fault is applied and then the current is ramped down at the time of stopping of the system. The different waveforms are studied in the rectifier and inverter scope. The waveforms reproduced are as follows:-

Fig 10: AC and DC Fault Current v/s time

At t=0.7s dc fault is applied and the fault current increases to 7500A with the transient reaching 0A at t=0.725s and then slightly increases to 1000A and then extinguishes at t=0.75s. The ac fault current remains 0A.

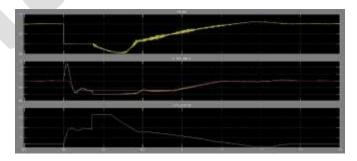

Fig. 11:  $V_{dL}$ ,  $I_d$  and alpha\_order v/s time waveforms for Rectifier

Fig. 12: V<sub>dL</sub>, I<sub>d</sub> and alpha\_order v/s time waveforms for Inverter

At t = 0.7 s, the dc fault is applied and the dc current at rectifier increases to 2.2 pu and at inverter drops to zero but the dc voltage at rectifier and inverter falls to zero. This Voltage Dependent Current Order Limiter (VDCOL) and the DC Fault protection detects the DC voltage drop and hence reduces the reference current at both the rectifier and inverter to 0.3 pu. A DC current flows between the line to ground fault. Then, at t = 0.77 s, a low DC voltage is detected by the DC fault protection circuit which forces the rectifier and inverter firing angles  $\alpha$  to 166 and 92 degrees respectively. The rectifier then operates in inverter mode and inverter in rectifier mode due to which the energy stored in the lie is returned to the ac system which forces the dc fault to extinguish also the line voltage becomes negative and reaches the maximum value of -0.5 pu. Then at t=0.82s the firing angle of rectifier decreases and that of inverter increases due to which dc current increases to 0.3pu with voltage crossing 0pu. Then at t=0.9s the current reference is then ramped and reaches the value of 1pu and the dc current and voltages increases with the ramp. Now the dc voltage and dc current takes a shoot to 1.1 pu then reaches the value of 1 pu between 1.18 s and 1.25 s in both rectifier and inverter.

Fig.13: AC voltage and inverter v/s time on Rectifier Side

Fig.14: AC voltage and current v/s time on Inverter Side

At t=0.7s,  $V_{abc\_r}$  decreases to 0.7 pu and  $V_{abc\_i}$  increases to 1.3pu but  $I_{abc\_r}$  increases to 25 pu/100 MVA and  $I_{abc\_i}$  decreases to 1pi/100MVA. Then at t=0.73s,  $V_{abc\_r}$  increases to 1.1pu and  $V_{abc\_i}$  decreases to 1.1pu and  $I_{abc\_r}$  decreases to 2 pu/100 MVA and  $I_{abc\_i}$  increases to 2 pu/100 MVA. At t=0.75s, both  $V_{abc\_r}$  and  $V_{abc\_i}$  remains same and  $I_{abc\_r}$  increases to 5 pu/100 MVA and  $I_{abc\_i}$  decreases to 0.5 pu/100 MVA. At t=0.85s,  $V_{abc\_r}$  and  $V_{abc\_i}$  decreases to 0.95pu and 1.05pu respectively and  $I_{abc\_i}$  and  $I_{abc\_i}$  increases to 10pu/100 MVA and 4 pu/100 MVA respectively. At t=1.2s, both  $V_{abc\_r}$  and  $V_{abc\_i}$  increases to 1 pu and  $V_{abc\_i}$  increases to 13 pu/100 MVA.

#### **CONCLUSION**

This paper concludes with the observation that whenever the system is simulated, the controller increases the reference current slowly with the ramp so that transient surges are prevented from occurring so that the dc current and voltage increases with the reference current and becomes constant at the steady state. Also if any fault occurs in the HVDC system the system detects the fault and extinguishes the fault automatically without changing the system parameters making the system stable.

#### **REFERENCES:**

- [1] "ABB opens era of power superhighways".

- [2] ^ "High Voltage Direct Current (HVDC) Transmission Super Highway Benefits to the Plains and Southeast".

- [3] "Wind Power 'Superhighway' Could Help Transform Panhandle Into U.S. Energy Hub".

- [4] "The Governance of Energy Megaprojects: Politics, Hubris and Energy Security".

- [5] Arrillaga, Jos; High Voltage Direct Current Transmission, second edition, Institution of Electrical Engineers, ISBN 0 85296 941 4, 1998.

- [6] Narain G. Hingorani in IEEE Spectrum magazine, 1996. Archived February 8, 2014, at the Wayback Machine.

- [7] ABB HVDC website.

- [8] Edison Tech Center Lauffen to Frankfurt 1891 The beginning of modern electric power in the world

- [9] Alfred Still, Overhead Electric Power Transmission, McGraw Hill, 1913 page 145, available from the Internet Archive

- [10] MATHWORKS website

- [11] Arrilaga, J., High Voltage Direct Current Transmission, IEEE® Power Engineering Series 6, Peter Peregrinus, Ltd., 1983

- [12] Jidong Zhang, Lars Dofnas, "A Novel Method to Mitigate Commutation Failures in HVDC Systems," Proceedings PowerCon 2002. International Conference on, Volume: 1, 13–17 Oct. 2002, pp. 51–56

- [13] A Textbook on Power System Engineering by A. Chakrabarti, M.L. Soni, P.V. Gupta, U.S. Bhatnagar; Dhanpat Rai & Co.,2014, Pg; 346

- [14] Arrillaga, Jos; High Voltage Direct Current Transmission, second edition, Institution of Electrical Engineers, <u>ISBN 0 85296 941</u> 4, 1998