# A NEW THREE PHASE SINGLE STAGE RECTIFIER

# THENE RAMABABU<sup>1</sup> & A SURYANARAYANA<sup>2</sup>

<sup>1</sup>M.Tech Student Scholar, Nova College of Engineering & Technology, Hyderabad, India <sup>2</sup>Assistant Professor, Nova College of Engineering & Technology, Hyderabad, India

# ABSTRACT

A new three-phase single-stage rectifier is proposed in this paper. The features of the proposed rectifier are that produce input currents that does not have dead time regions and an output current that can be continuous when the converter is operating from maximum load to at least half of the load. In this paper, the operation of the new converter is explained, its features and design are discussed in results, and its operation is confirmed with experimental results obtained from a prototype.

**KEYWORDS:** AC–DC Power Conversion, Single-Stage Powerfactor Correction (SSPFC), Three-Level Converters, Three-Phase

### I. INTRODUCTION

This approach, however, is expensive and complicated as it needs ten active switches along with associated gate drive and control circuitry. Moreover, the converter must be operated with sophisticated control methods that require the converters. Proposed alternatives have included: 1) using three separate ac-dc boost converter modules [2]; 2) using a reduced switch ac-dc converter [3]; and 3) using a single-switch boost converter [4]. Two separate switch-mode converters are still needed, however, to perform three-phase ac-dc power conversion with transformer isolation.

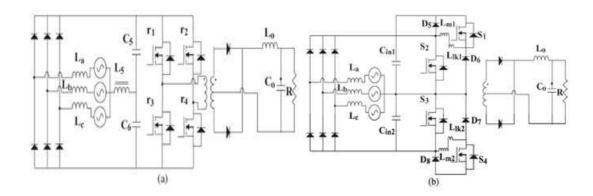

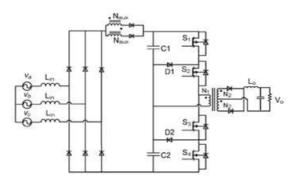

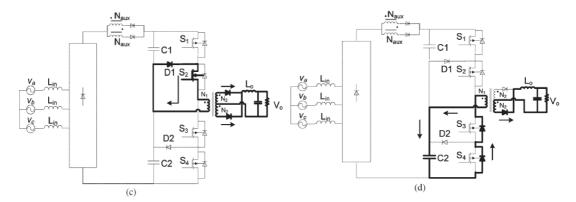

Researchers have tried to further reduce the cost and complexity associated with single-phase [5]–[12] and three-phase [13]–[24] ac-dc power conversion and PFC by proposing single-stage converters that integrate the functions of PFC and isolated dc-dc conversion in a single power converter. Several examples of three-phase single-stage converters are shown in Figure 1. Previously proposed three-phase single-stage ac-dc con- verters, however, have at least one of the following drawbacks that have limited their widespread use.

Figure 1: Three-Phase Single-Stage Ac-Dc Converters. (a) Three-Phase Reduced Switch ac-dc Converter [16]. (b) [17]. (c) [18]

• Input currents are distorted and contain a significant amount of low-frequency harmonics because the converter has difficulty performing PFC and dc-dc conversion simultaneously [16].

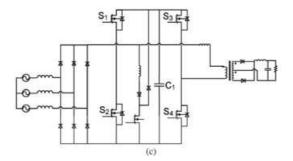

**Figure 2: Proposed Converter**

Converter must be controlled using very sophisticated techniques and/or nonstandard techniques [5]–[11]. This is particularly of resonant type converter that need variable switching frequency control methods to operate. 5) Output inductor must be very low, which makes the output current to be discontinuous. This paper presents a new three-phase, single-stage rectifier that does not have any of these drawbacks. In this paper, the operation of the new converter is explained, its features and design are discussed in results, and its operation is confirmed with experimental results obtained from a prototype.

### **II. CONVERTER OPERATION**

The converter transformer to cancel the dc bus capacitor voltage so that the voltage that appears across the diode bridge output is zero. This voltage cancellation occurs whenever there is voltage across the main transformer winding and current in the input inductors rises when it does. When there is no voltage across the main transformer primary winding, the total voltage across the dc bus capacitors appears at the output of the diode bridge; since this voltage is greater than the input voltage, the input currents falls. If the input currents are discontinuous, they will be naturally nearly sinusoidal (when filtered) and in phase with the input voltages. To simplify the analysis, the following assumptions are made: 1) The input voltage value can be considered as constant within a switching period as the period of the three-phase voltage supply is much longer than the switching period; 2) All devices are ideal; 3) The currents in inductors La = Lb = Lc = L in are *iLa*, *iLb*, *iLc* and have the same amplitude; 4) The dc bus voltage has no ripple.

Figure 3: Typical Waveforms Describing the Modes of Operation

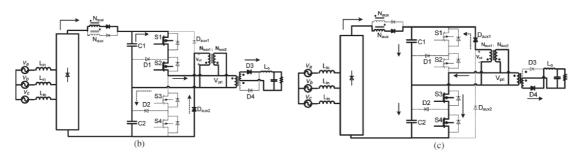

The equivalent circuit in each stage is shown in Figure 4. The converter goes through the following modes of operation in a half switching cycle.

Due to magnetic coupling, a voltage appears across one of the auxiliary windings and cancels the total dc bus capacitor voltage; the voltage at the diode bridge output is zero, and the input currents rise. Due to the high switching frequency, the supply voltage is assumed constant within a switching cycle. In this mode, the three-phase input current equations are as follows:

As it can be seen from (1), the equations that describe the relation between the current and voltage of input currents *iLa*, *iLb*, and *iLc are* the same, but with different notation. Therefore, instead of using terms with subscripts a, b, and c in this paper, a general notation  $\rightarrow$  is defined so that only one equation is written instead of three equations. Equation (1) can thus be rewritten as,

The auxiliary inductor current increases during this mode, and the following expression can be written:

Figure 4: Modes of Operation. (a) Mode 1 (t0 < t < t1). (b) Mode 2 (t1 < t < t2). (c) Mode 3 (t2 < t < t3). (d) Mode 4 (t3 < t < t4)

At the end of Mode I, the current in the auxiliary inductor Lin, during the kth interval is

Where *vk* is the average value of the supply voltage in the interval k, D is the duty cycle, and *fsw* is the switching frequency. Since the converter operates with a steady-state duty cycle D that is constant throughout the line cycle, the peak value of an input inductor current at the end of this mode is dependent only on the supply voltage.

The output inductor current can be expressed as

If it is assumed that the output inductor current is continuous, then the following expression for peakto- peak ripple can be derived:

*Mode 2* (t1 < t < t2) [*Figure. 4(b)*]: In this mode, *S*1 is OFF, and *S*2 remains ON. The energy stored in the auxiliary inductor during the previous mode is completely transferred into the dclink capacitor. The amount of stored energy in the auxiliary inductor depends upon the rectified supply voltage. This mode ends when the auxiliary inductor current reaches zero. Also, during this mode, the load inductor current freewheels in the secondary of the transformer. The voltage across the auxiliary inductors in Mode II is  $/-\rightarrow Vk/ - V$ bus, thus, the auxiliary current expression is as follows:

$$\frac{d\overline{l}_{L_{in}}}{dt} = \frac{|\overline{v_k}| - v_{bus}}{L_{in}}$$

$$\overline{l}_{L_{in},k}(t) = \overline{l}_{L_{in},k}, \max - \frac{v_{bus} - |\overline{v_k}|}{L_{in}} \cdot t \dots$$

(7)

This mode ends when the auxiliary inductor current reaches zero. This mode lasts for  $\Delta s_{,k/2fsw}$  amount of time; using (4), the following expression can be found:

Where  $\Delta s, k$  is the normalized period of Mode II. Equation (8) shows that the duration of this mode is time varying along one ac line period. In order to ensure a discontinuous input current, the normalized period  $\Delta s, k$  must satisfy the expression  $D+\Delta s, k < 1$  for any interval k and any load conditions. Using (8), this constraint can be written as

On the other hand, the load inductor current freewheels in the secondary of the transformer, which defines a voltage across the load filter inductor equal to -VL; therefore, the load inductor current is given by

$$i_{L_o}(t) = i_{L_o,max} - \frac{v_L}{L_o}t.....(10)$$

$$\Delta i_{L_0} = \frac{v_L}{L_0} - \frac{1 - D}{2f_{\text{SW}}}.....(11)$$

Consequently, the following expression can be derived from (6) and (11)

$$v_o = \frac{v_{bus}}{2N} D.....(12)$$

There is no energy transferred to the dc bus capacitors. *Mode 4* (t3 < t < t4) [*Figure 4*(d)]:. For the remainder of the switching cycle, the converter goes through Modes 1 to 4, but with S3 and S4 ON instead of S1 and S2. The rectified supply voltage of each phase, and the current flowing through each inductor increases.

*Mode* 6 (t5 < t < t6): In this mode, S3 is ON, and S4 is OFF. The energy stored in the auxiliary inductors during the previous mode is completely transferred into the dc-link capacitor.

*Mode* 7 (t6 < t < t7): In this mode, S4 is OFF, and the primary current of the main transformer circulates through the diode D2 and S3. The output inductor current also freewheels in the secondary of the transformer during this mode.

*Mode* 8 (t7 < t < t8): In this mode, S3 and S4 are OFF, and the primary current of the transformer charges the capacitor C1 through the body diodes of S1 and S2. Switches S1 and S2 are switched on at the end of this mode.

Output voltage regulation can be done by standard control methods that control duty cycle D. Duty cycle, D in (4), is defined as the time when *S*1 and *S*2 are both ON during the first half cycle or when *S*3 and *S*4 are both ON during the second half cycle. These two cases correspond to energy transfermodes of operation. Any control method that can be used to regulate a two-level full-bridge converter by controlling D can be used to regulate the proposed converter; the only difference is how the gating signals are implemented. For example, the control for the proposed converter can be implemented with a conventional phase-shift PWM controller, and some logic can be added to the output of the controller to generate the appropriate gating signals.

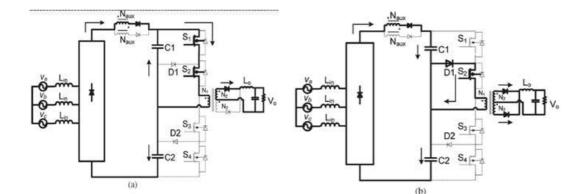

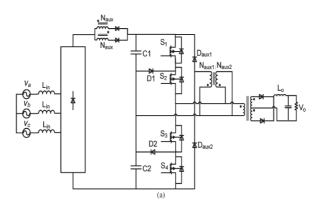

Various such techniques have been proposed in the literature, including techniques that sense the capacitor voltages and adjust the duty cycle of the converter switches appropriately. For this work, an auxiliary circuit that consists of a transformer with a turns ratio of Naux1/Naux2 = 1 and two diodes Daux1 and Daux2 was used, as now shown in Figure 5(a) [25]. This circuit is very simple, small, and handles only a small fraction of the overall power that is processed by the converter so that the low current rated diodes can be used (<1 A) and a small core can be used for the transformer. It should be noted that the auxiliary circuit can take care of the voltage balancing, which allows a standard controller to be used for the full bridge.

The basic principle behind the auxiliary circuit is that if the voltage across one capacitor begins to be greater than the other by more than a diode drop, then one of the diodes begins to conduct as energy is transferred away from the capacitor with the higher voltage. Since the auxiliary circuit does not allow for large differences in bus capacitor voltage, the amount of energy that needs to be transferred away at any given time is small. When the auxiliary circuit is added to the main circuit, it is most likely to come into play during Modes 1 and 5 of operation as this is when the most current will flow through one of the bus capacitors. The auxiliary circuit works as follows during these modes.

*Mode 1* (t0 < t < t1) [*Figure 5(b)*]: During this mode, switches S1 and S2 are ON, and energy from the dc-link capacitor C1 flows to the output load. Since the auxiliary winding generates a voltage that is equal to the total dc-link capacitor voltage (sum of C1 and C2), the voltage across the auxiliary inductor is the rectified supply voltage. This allows energy to flow from the ac mains into the auxiliary inductor during this mode, and the auxiliary inductor current increases.

At the beginning of this interval, if there exists any unbalance between the voltages of the two dc-bus capacitors, such that VC1 > VC2, the auxiliary circuit starts conducting through diode *D*aux2 to balance the voltage difference across the *C*1 and *C*2. To balance the voltage difference across the capacitors.

### **III. STEADY-STATE ANALYSIS**

In order to develop a procedure that can be used to design the proposed converter, the steady-state operation of the converter must be analyzed to determine its behavior for any given set of specifications (line-to-line input voltage *Vll*, rms, output voltage *Vo*, output current *Io*, and switching frequency *fsw*) and any given set of component values input inductors La = Lb = Lc = Lin, duty ratio D, transformer turns ratio N = n1/n2, output inductor *Lo*). Important converter characteristics can be determined after the analysis has been performed and then used to develop the design procedure.

Figure 5: (a) Proposed Single-Stage Three-Level Converter with Auxiliary Circuit (b) Mode 1 with Auxiliary Circuit (c) Mode 5 with auxiliary circuit.

Such as input current can be determined. Unlike a conventional two-stage converter, a single-stage converter is not solely regulated by the ac-dc boost PFC stage and cannot be purposefully kept constant. This voltage can be derived by noting that energy equilibrium must exist for storage capacitor when the converter is in steady-state operation.

The energy pumped into the capacitor from the input section must be equal to the energy that provides to the output, so that the net dc current flowing in and out of must be zero during a half-line cycle. However, this cannot be determined by an equation with a closed-form solution due to the various possible combinations of input and output modes of operation, but must instead be determined using a computer program.

Magnetizing current, then for an operating point with given input voltage Vin, output voltage VL, switching frequency *fsw*, input inductor *L*in, output inductor *Lo*, transformer turns ratio N = N pri/Nsec, and output current *Io* can be determined as follows:

- 1) Select the set of specifications and components values to be considered. Assume a duty cycle D as an initial "guess"; (i.e., D = 0.5) to start the process of determining a corresponding dc bus capacitor voltage *V*bus.

- 2) Assume that the output current is continuous; then, use (12) to find Vbus

$$v_{bus} = \frac{2v_0 N}{D}.....(13)$$

3) With this value of  $V_{\text{bus}}$ , verify that the output current is continuous by seeing that the peak output current ripple does not exceed the average current  $I_0$

$$\frac{1}{2} \frac{\frac{v_{bus}}{2N} - v_o}{L_o} \cdot \frac{D}{2f_{sw}} < I_o \dots \dots$$

(14)

If this relation is satisfied, then *V*bus is equal to the value determined in (13). If not, then the output current is discontinuous and  $V_{\text{bus}}$  must be determined using (15), which has been derived for discontinuous current mode (DCM)

$$v_{bus} = 2N \frac{v_o - \sqrt{v_o^2 + \frac{16p_o L_o f_{sw}}{D^2}}}{2} \dots$$

(15)

4) With *V*bus known, find the average current that flows out of capacitors during a half-line cycle using either (16) for continuous current mode (CCM) or (17) for DCM

$$I_{cb,out-avg} = \frac{D^2}{4NL_o f_{sw}} \left(\frac{v_{bus}}{2N} - v_o\right) \dots$$

(17)

Figure 6: Procedure of Steady-State Analysis for Determining the Dc Bus Voltage

5) Determine the average current that is fed from the input to capacitors during a half-line cycle using (17)

$$I_{cb,in-avg} = 3 * \left( 2f_{in} \sum_{k=0}^{m} \int_{t^*}^{t_k} \left[ \frac{v_{in,k} - v_{bus}}{L_{in}} (t - t^*) + I_{in,k}^* \right] dt \right).$$

(18)

Where I\*in,k is the peak input current value during a switching cycle k. If (18) is equal to (14) or (15), then the converter is confirmed to be operating under steady-state conditions, and the value of *V*bus that has been calculated is valid. If not, then the operating point for which is to be determined is not a valid operating point, and the procedure must be repeated for a different value of D. The flowchart in Figure 6 shows the procedure for the steady-state analysis, which can be implemented in a computer program.

### **IV. CONVERTER CHARACTERISTICS**

The procedure discussed in Section III can be repeated to determine Vbus (or any other parameter) for other operating points, in order for curves to be generated for analysis and design purposes. The converter operating characteristics for any given input and output voltage are dependent on three key parameters: transformer turns ratio N, input inductance *L*aux, and output *Lo*. In this section, the effect of each of these parameters is examined with graphs of characteristic curves that have been generated with a computer program based on the procedure described above.

#### A. Effect of Output Inductor Value Lo on DC Bus Voltage Vbus

It can be seen from Figure 7(a) that varying *Lo* (but keeping all the other parameters fixed) has a slight effect on *V*bus for higher output loads when the output is operating in CCM, but does so at lower output loads when the output is in DCM. This is because more energy can be transferred from the dc bus capacitor to the output when the output inductor current is discontinuous rather than continuous, for the same amount of average output current.

#### B. Effect of Input Inductor Value Lin on DC Bus Voltage Vbus

Similar to what was stated above for the output inductor, less energy is transferred from the input to the dc bus when the inductor is larger and the current is more likely to approach the boundary of CCM and DCM.

#### C. Effect of Transformer Turns Ratio N on DC Bus Voltage

Pump out so much energy that the energy equilibrium at capacitor will result in a very low dc bus voltage that will in turn force the converter to operate with an output voltage that will always be lower than the required value, particularly under heavy load conditions. Likewise, if N is very high, then C1 and C2 may pump out so little energy that that the energy equilibrium C1 and C2 will result in a very high dc bus voltage that will in turn force the converter to operate with an output voltage that will always be higher than the required value, particularly under light load conditions.

#### D. Effect of Input Voltage Vin on DC Bus Voltage Vbus

Figure 7(d) shows the effect of input voltage on dc bus voltage. As can be seen, increasing the input voltage increases the dc bus voltage. This is because more energy is pumped into the capacitors when the input voltage is at high line

### V. CONVERTER DESIGN

A procedure for the design of the converter is presented in this section and is demonstrated with an example. The following criteria should be considered when trying to design the converter: 1) The energy-storage capacitor voltage *V*bus should not be excessive. 1) The value of *V*bus should be kept to below. 800 V if possible so that the use of bulkier, more expensive capacitors can be avoided.

Figure7: Steady State Characteristic Curves (*V*in = 208 *V*rms, *Vo* = 48 V, *Fsw* = 50 Khz). (A) Effect of Output Inductor Value *Lo* On Dc Bus Voltage. (B) Effect of Input Inductor Value *L*in on Dc Bus Voltage. (C) Effect of Transformer Ratio Value N on Dc Bus Voltage. (D) Effect of Input Voltage *V*in on Dc Bus Voltage

- 1) Excessive peak output and input currents should be avoided if possible.

- The input line current must satisfy the necessary regulatory agency requirements of harmonic content such as IEC1000-3-2 Class A. can be designed. The converter is to be designed with the following parameters for the example:

Input voltage :  $Vin = 208 \pm 10\% Vl - l$ ,rms Output voltage : Vrmo = 48 VMaximum output power : Po = 1500 WSwitching frequency : fsw = 1/Tsw = 50 kHz

Maximum capacitor voltage : (for each capacitor)450 V Input current harmonics : EN61000 - 3 - 2for Class A electrical equipment.

Discharge the bus capacitors. If N is high, the primary current may be too high and thus more conduction losses. N should be high enough to reduce the circulating primary current, then the primary current that is available to discharge the dc-link capacitors may be low and thus Vbus may become excessive under certain operating conditions (i.e., high line). Equation (10) shows the relation between Vbus, D, Vo and N. The minimum value of N can be found by considering the case when the converter must operate with minimum input line and, thus, minimum primary side dc bus voltage Vbus, min and maximum duty cycle Dmax.

If the converter can produce the required output voltage and can operate with discontinuous input and continuous output currents in this case, then it can do so for all cases

Finding the proper value of N can be done with a computer program. As described in Section III, Vbus is determined by the converter parameters for various values of Lin and with fixed values of N. it should be the highest value for which valid operating points exist for the two most extreme line and load conditions: high line, light load and low line, full load. N has been chosen to be 3 for given example.

With a value of N = 3, Vo = 48, and Dmax = 0.75 the actual value of V bus can now be determined by using computer program which gives V bus, min = 384 V.

*Step 2—Determine Value for Input Inductor Lin:* The value for *L*in should be low enough to ensure that the input current is fully discontinuous under all operating conditions, but not so low as to result in excessively high peak currents. This can be done using the computer program with the following equations, which are based on the descriptions given in Section III.

For the case where *L*in is such that the input current remains discontinuous for all operating conditions, then the average input power can be expressed as

$$P_{in} = \frac{3}{\frac{\pi}{2}} * \left( \frac{1}{T_{su}} \int_{0}^{T_{su}} |v_{s,k}| \, i_{s,k} d_{w_k} t \right)$$

$$= \frac{3}{\frac{\pi}{2}} \cdot \frac{1}{f_{sn}} \sum_{k=0}^{f_{sn}-1} |v_{s,k}| i_{s,k} \dots$$

(20)

Where fsu is the input ac frequency and fsn = 2fsw/fsu and

$$i_{s,k} = \left(\frac{D + \Delta_s}{2}\right) i_{L_{in,max}}$$

By substituting the value of is, k(21), Pin can be expressed as

$$P_{in} = \frac{3}{\frac{\pi}{2}} \cdot \frac{1}{f_{sn}} \sum_{k=0}^{f_{sn}-1} |v_{s,k}| i_{s,k}$$

$$= \frac{3.D^2}{8 \cdot \frac{\pi}{2} \cdot L_{in} \cdot f_{sw}} \cdot \frac{1}{f_{sn}} \sum_{k=0}^{f_{sn}-1} \frac{|v_{s,k}|^2}{1 - \frac{|v_{s,k}|}{v_{bus}}} \dots$$

...22

By assuming the Pin = Po, Lin can be achieved

The worst case to be considered is the case when the converter operates with minimum input voltage and maximum load since if the input current is discontinuous under these conditions, it will be discontinuous for all other operating conditions, and thus an excellent power factor will be achieved. In this case, Vin = 188 Vphase,rms and Vbus = 384 V as calculated in Step 1 are used to determine Lin at the boundary condition for the input section, and D = Dmax = 0.75; assuming the converter to be lossless, Pin = Po = 1500Wis used. The value of  $Lin = 68 \mu$ H is found from the computer program. For this design, Lin = 65  $\mu$ H is used.

#### Step 3: Determine Value for Output Inductor Lo

The output inductor can be designed in such a way that the output current to be in DCM or CCM or semicontinuous mode (SCCM). Therefore, there are three options to design output inductor.

The maximum value of *Lo* should be the value of *Lo* with which the converter's output current will be on the boundary between being continuous and discontinuous when the converter is operating with minimum input voltage, maximum duty cycle (*D*max), and full load (*Po*, max). If this condition is met, then the output current will be dis continuous for all other converter's operating conditions. The maximum value of *Lo* can therefore be determined to be

$$L_{o,max} = \frac{v_o^2}{P_{o,max}} \cdot \frac{(1 - D_{max})}{2} \cdot \frac{T_{sw}}{2} \dots$$

(24)

This results in a very high output ripple so that secondary diodes with high peak current ratings and large output capacitors to filter the ripple are needed.

2) *Output Inductor for Full Output CCM:* For having CCM at output, the minimum value of *Lo* should be the value of *Lo* with which the converter's output current will be continuous on the when the converter is operating with maximum input voltage, minimum duty cycle (*D*min), and minimum load (10% of *Po*,max). If this condition is met, then the output current will be continuous for all other converter's operating conditions. The minimum value of *Lo* can therefore be determined to be

$$L_{o,min} \ge \frac{v_o^2}{0.1 \cdot P_{o,max}} \cdot \frac{(1 - D_{min})}{2} \cdot \frac{T_{sw}}{2} \dots$$

(25)

This results in a low ripple at output and low peak current rating for secondary diodes, and consequently lower output capacitor needs to filter the ripple. However, it has a major drawback. Bus voltage *V*bus is dependent on the current that is flowing in and out of the bus capacitor, which is, in turn, dependent on the output inductor currents. When the output current is CCM, then the dc bus voltage is dependent on the load, and it is not constant. This results in a high dc bus voltage at light load condition which needs to use high voltage dc bus capacitor and switches with higher rating. There are two solutions for this problem.

### a) DC Bus Voltage Control by Changing Auxiliary Winding Turns Ratio

The auxiliary winding turns ratio can be designed in a way that does not completely cancel out the voltage across the dc bus capacitor. This reduces the amount of voltage placed across the input inductor and thus reduces the amount of energy pumped into the input inductor. Consequently, the reduced energy in the input inductor affects the energy equilibrium of the dc bus capacitor and thus reduces the dc bus voltage.

Reducing the number of auxiliary winding turns introduces dead band regions in the zero-crossing sections of the input current waveform. This is because the diode-bridge diodes are reverse biased when the input voltage is low, and current is not allowed to flow in the input inductor as the dc bus voltage is not fully cancelled out by the auxiliary winding [26]. Therefore, there is a trade off between the input pf and the dc bus voltage

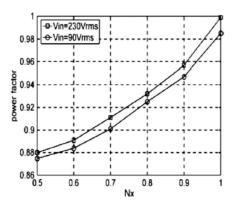

reduction [27]. The auxiliary winding turns ratio should be selected to satisfy both the IEC1000-3-2 standards and reduce the dc bus voltage. For example, if choose Naux = 1.7 instead of 2, the bus voltage decreases 50 V. Figure 8 shows the variation of power factor versus variation of auxiliary winding turns ratio.

#### b) Output Inductor for Semi-CCM

This method is a compromising solution to have a continuous current at output for almost loads in one hand and preventing high dc bus voltage on the other hand. The output inductor should be designed so that the output current is made to be continuous under most operating conditions. The minimum value of *Lo* should be the value of *Lo* with which the converter's output current will be continuous on the when the converter is operating with maximum input voltage, minimum duty cycle (*D*min), and at least 50% of maximum load. The minimum value of *Lo* can therefore be determined to be

Figure 8: Variation of Pf for Different Values of Auxiliary Winding Turns Ratio [26]

A New Three Phase Single Stage Rectifier

$$L_{o,min} \ge \frac{v_o^2}{0.5 \cdot P_{o,max}} \cdot \frac{(1 - D_m)}{2} \cdot \frac{T_{sw}}{2} \dots$$

...(26)

In this paper, SCCM mode for the output current is assumed. Substituting  $Po, \max = 1500$  W, Vo = 48 V,  $Tsw = 20 \ \mu$ s, and Dm = 0.5 gives  $Lo, \min = 7 \ \mu$ H and the value of Lo should be larger to provide some margin. The value of Lo should be larger to provide some margin. On the other hand, according to Figure 7(a), the value of Lo cannot be too high as the dc bus voltage of the converter will become excessive; a value of

$Lo = 11 \,\mu\text{H}$  is chosen

### VI. EXPERIMENTAL RESULTS

An experimental prototype of the proposed converter was built to confirm its feasibility. The prototype was designed according to the following specifications:

Input voltage  $Vin = 208 \pm 10\%$  Vrms (line-line)

Output voltage Vo = 48 V

Output power Po = 1.5 KW

Switching frequency fsw = 50 kHz.

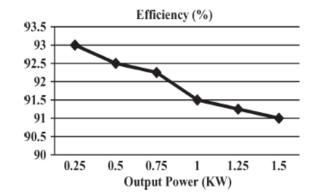

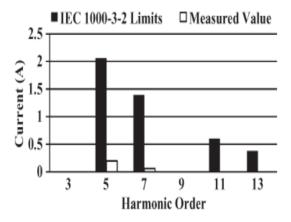

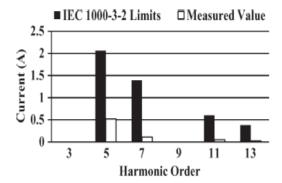

The main switches are FDL100N50F, and diodes are UF1006DICT. The input inductors are  $Labc = Lin = 60 \mu$ H, the dc link capacitors are C1,  $C2 = 2200 \mu$ F, and the output inductor is  $Lo = 11 \mu$ H. The auxiliary transformer ratio is 1: 2, and the main transformer ratio is 3 : 1. Typical converter waveforms are shown in Figure 9–11 for different loads. It can be seen that the proposed converter can operate with no dead band regions, that it is a multilevel full-bridge converter, that the switch stress is half the dc bus voltage, and that it can operate with a continuous output current, unlike most other converters of the same type. The lack of dead band regions in the input current waveforms is due to the greater flexibility that is allowed by the proposed converter's multilevel structure—there is less need to distort the input current to try to prevent the dc bus voltage from becoming excessive. It should be noted that, like other previously proposed converters with discontinuous input currents, the high input current ripple is a source of EMI. Suggestions for dealing with EMI issues in these converters can be found in [28]. Figure 12 shows the efficiency of the converter at different values of the output power. Figures 13 and 14 show the input current harmonics a Po = 1500 W and Po = 750 W when Po = 1500 W when Vin = 220 Vl-lrms. It can be seen that the converter's harmonics are below the harmonic levels that are specified by the IEC 1000-3-2 standard.

The efficiency measured from the converter at light load was about 93% and for full load was 91% as shown in Figure 10. In multilevel converters such as the proposed converter, the voltage stresses of their power switches are only half of the input voltage and not the full input voltage as is the case for two-level converters. This means that less energy is required to discharge the output capacitances of switch MOSFET devices, and thus they can operate with fewer switching losses and a wider load range for zero-voltage switching (ZVS) than two level converters. Compared to other multilevel converters such as the ones proposed in [17] and [22], the proposed converter is simpler (in terms of topology and in capacitor voltage balancing), has better lighter load efficiency (since its switches are exposed to less voltage and thus it is easier to discharge switch capacitances during switch turn-on with less primary current), and can operate with less output inductor current ripple, even continuous output inductor current at heavier loads. In terms of total harmonic distortion

(THD), the proposed converter has low THD, less than 7%, which is similar to the converters in [17] and [22].

# VII. CONCLUSIONS

The proposed converter has the following features.

- Proposed converter has an auxiliary circuit that can cancel the capacitor voltage in which way the input inductor acts as a boost inductor to have a single-stage PFC.

- Proposed converter can operate with lower peak voltage stresses across the switches and the dc bus capacitors as it is a three-level converter. This allows for greater flexibility in the design of the converter and ultimately improved performance.

- Proposed converter can operate with an input current harmonic content that meets the EN61000-3-2 Class A standard.

- Output inductor of the proposed converter can be designed to work in CCM mode over a wide range of load variation and input voltage. This results in a lower output inductor current ripple than that found in other two-level single stage converter, which ultimately results in lower peak current stresses for the secondary components.

Figure 9: Experimental Results (A) Input Current and Voltage (For Two Phases) (V: 100 V/Div, I: 15 A/Div).

(B) Output Inductor Current (I: 15 A/Div., T: 5 Ms/Div.). (C) Primary Voltage of the Main Transformer (V: 150 V/Div., T: 5 Ms/Div). (D) Bottom Switch Voltages Vds4 and Vds3 (V: 150 V/Div, T: 5 Ms/Div)

Figure 10: Experimental Results For 50% of Full Load. (A) Input Current and Voltage (For Two Phases) (V: 100 V/Div, I: 10 A/Div). (B) Output Inductor Current (I:15 A/Div., T : 5 Ms/Div.). (C) Primary Voltage of the Main Transformer (V: 200 V/Div., T : 5 Ms/Div.). (D) Bottom Switch Voltages Vds4 And Vds3 (V: 200 V/Div., T : 5 Ms/Div.)

Figure 11: Experimental Results For 25% of Full Load. (A) Input Current and Voltage (For Two Phases) (V: 100 V/Div, I: 10 A/Div). (B) Output Inductor Current (I: 10 A/Div., T: 5µs/Div.). (C) Primary Voltage Of The Main Transformer (V: 200 V/Div., T: 5 Ms/Div.). (D) Bottom Switch Voltages Vds4 and Vds3 (V: 200 V/Div., T: 5 Ms/Div)

Figure 12: Converter Efficiency with Input Voltage VLL-rms = 220 V

Figure 13: Input Current Harmonic at Vin = 220 Vrms(*l* – *l*), *Po* = 1.5 KW Compared to IEC1000-3-2 Class A Standard Figure

Figure 14: Input current harmonic at Vin = 220 Vrms(l - l), Po = 0.75 KW compared to IEC1000-3-2 Class A standard

• Converter is simple and can be implemented with a simple passive auxiliary circuit to balance the dc bus capacitor voltages.

# REFERENCES

- P. D. Ziogas, Y. Kang, and V. R. Stefanovic, "PWM control techniques for rectifier filter minimization," *IEEE Trans. Ind. Appl.*, vol. IA-21, no. 5, pp. 1206–1214, Sep. 1985.

- 2. G. Spiazzi and F. C. Lee, "Implementation of single-phase boost powerfactor correction circuits in three-phase applications," *IEEE Trans. Ind. Electron.*, vol. 44, no. 3, pp. 365–371, Jun. 1997.

- B. Lin and D. P. Wu, "Implementation of three-phase power factor correction circuit with less power switches and current sensors," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 34, no. 2, pp. 64–670, Apr. 1998.

- 4. R. Prasad, P. D. Ziogas, and S. Manias, "An active power factor correction technique for three-phase diode rectifiers," in *IEEE Power Electron. Spec. Conf. Rec.*, 1989, pp. 58–66.

- 5. J. M. Kwon, W. Y. Choi, and B. H. Kwon, "Single-stage quasi-resonant flyback converter for a cost-effective PDP sustain power module," *IEEE Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2372–2377, Jun. 2011.

- 6. H. S. Ribeiro and B. V. Borges, "Analysis and design of high-efficiency full-bridge single-stage converter with reduced auxiliary components," *IEEE Trans. Power Electron.*, vol. 25, no. 7, pp. 1850–1862, Jul. 2010.

- H. L. Cheng, Y. C. Hsieh, and C. S. Lin, "A novel single-stage high-powerfactor ac/dc converter featuring high circuit efficiency," *IEEE Trans. Ind. Electron.*, vol. 58, no. 2, pp. 524–532, Feb. 2011.

- 8. B. Tamyurek and D. A. Torrey, "A three-phase unity power factor single stage ac-dc converter based on an interleaved fly back topology," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 308–318, Jan. 2011.

- 9. Y. Hung, F. Shyu, C. Lin, and Y. Lai, "New voltage balance technique for capacitors of symmetrical half-bridge converter with current mode control," in *Proc. 5th Int. Conf. PEDS*, 2003, pp. 365–369.

- 10. P. Das, S. Li, and G. Moschopoulos, "An improved ac-dc single-stage full bridge converter with reduced dc bus voltage," *IEEE Trans. Ind. Electron.*, vol. 56, no. 12, pp. 4882–4893, Dec. 2009.

- 11. M. K. Nalbant, "Power factor calculations and measurement," in *IEEE APEC Conf. Rec.*, 1990, pp. 543–552.