# Advanced High Speed Frequency to Voltage Converter for Industrial Controllers.

Ayyaj .I .Nadaf 1, Dr. P. P. Shaha2, Dr. M. K. Bhanarkar3 Department of Electronics, Shivaji University, Kolhapur1,3, Department of Electronics, Devchand College, Nipani2 ayyaz.nadaf@gmail.com.

**Abstract**— This paper presents utilization of on chip Pulse Width Modulation (PWM) for generating analog voltage. Industrial controllers or PLC requires digital to analog converters for process control. Many industrial devices like Variable Frequency Drive (VFD) work on standard analog input 0 to 10v. To communicate DAC modules and PLC special protocol are involved. It leads to time latency to get analog output. This paper represents without any protocol single digital output pin of PLC to give frequency to DAC module. This module converts those ranges of frequency signal to calibrated PWM to get analog output with low pass filter. With this module one can get analog voltage in standard range of 0 to 10v with ripple less than 0.1V. For This module can work in range of 1 kHz to 10 kHz.

**Keywords**— DAC, LOW PASS FILTER, PLC, PWM, PROTOCOL, VFD.

## INTRODUCTION

In Automated industry there are lots of process variable need to be controlled so as to get process under control. Simply saying there are lots of continuous signals need to monitor and control. Continuous actuators are major parts of the process. Today's continuous actuators are able to work on multiple standards like 4-20 mA,-10v to +10V DC, 0 to 10V DC. It is necessary to create interface between digital controllers and actuators. Industrial controller like PLC has capability to generate frequency signal. It's a need to create an interface can accept those frequency signals from PLC and generate 0 to 10V DC analog output. This analog output signal can then easily feed to industrial devices like VFD, PID controller etc.

In a typical PWM signal, the base frequency is fixed, but the pulse width is a variable or fixed. The pulse width is directly proportional to the amplitude of the original unmodulated signal. In other words, in a PWM signal, the frequency of the waveform is a constant while the duty cycle varies according to the amplitude of the original signal. A simple low pass filter is used to generate an output voltage directly proportional to the average time spent in the high level.

## RESEARCH PROBLEM

Many industrial devices work on standard analog input 0 to 10v. To communicate DAC modules and PLC special protocol are involved. It leads to time latency to get analog output. DAC using R-2R ladder requires more power, more no of components, uses more no of bits to achieve good resolution. Potentiometric DACs have excellent linearity but they are much expensive and available with limited no of bits. All these methods involve reference power supply.

#### RELATED WORK

$1.4V~13\mu W~83dB~DR~CT-\Sigma\Delta$  modulator with Dual-Slope quantizer and PWM DAC for bipotential signal acquisition. This paper presents the implementation and measurements of a novel ultra-low power low voltage multi-bit continuous-time sigma-delta (CT- $\Sigma\Delta$ ) modulator, whose quantizer and feedback DACs operate in the time domain [1]. A low power successive approximation A/D converter based on PWM technique, this paper introduces a new architecture for a simple, practical and high precision conversion and analysis with Fourier transform method [2]. An AC voltage standard based on a PWM based DAC. This paper describes a new AC voltage standard which uses a traceable DC voltage standard as an input and produces an AC output at an equivalent RMS voltage to 1  $\mu V/V$  uncertainty [3].

#### PWM BASED DAC APPROACH

Industrial controller requires converting of digital to analog signal with minimum settling time, less bulky system, and accurate result without investing in much cost in new modules. Some advantages of PWM based DAC systems are

- Single pin requirement from the microcontroller GPIO pins.

- Extremely low external component requirement, without severe precision requirement.

- Output resistance that is independent of input.

$$[ScaleCount] = \left[ \frac{ScaleMaxVa lue}{Digital Input Max Count} \right] \times Digital Input$$

As the scaling factor is a constant for a given DAC implementation, it can be precomputed and stored for use. e.g. In 8 bit PWM max count can be given is 255. In this case we need to read input frequency by means of timer, this is the digital count. For measuring of input frequency max up to 100 kHz. Timer need to select must have time base of 0.01 mS.

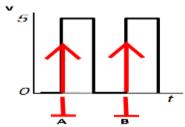

Figure 1: Input frequency signal.

Here to measure frequency of input signal; it is necessary to start timer at first rising edge A and stop timer at second rising edge B. Frequency of input signal is reciprocal of timing count difference between B and A multiplied by time base for timer. This digital input is must be calibrated for full scale 100% duty cycle. For example digital count of input frequency is 46015; max count possible with 16 bit variable register is 64536. If duty cycles register is 8 bit so for 100% duty cycle count should be 255. Therefore

[ScaleCount] =

$$\left[\frac{255}{65536}\right] \times \text{Digital Input}$$

[Scale Count]=0.003890 × Digital Input.

0.003890 is precomputed constant based on calibration factors.

Scale Count is same to Duty Cycle count.

Duty Cycle =  $[0.003890] \times 46015$ .

Duty Cycle= 179; it is 70% of total 100% duty ratio.

The PWM/DAC approach is not new, but performance limitations have historically confined its use to low-resolution, low-bandwidth applications. The performance of the method relates directly to the ability of the low pass filter to remove the high frequency components of the PWM signal. Use of filter with too low a cut-off frequency, and DAC bandwidth suffers. Use a filter with too high a cut-off frequency DAC resolution suffers but one way to improve both of these problems is to increase the frequency of the PWM.

dac resolution:

$$Ao = \left[\frac{Di}{2^{N}}\right] \times Ref$$

Where:

Ao = Analog output.

Di = Digital input as a duty cycle count.

N = Number of digital input bits (resolution)

Ref = Reference Value (full scale).

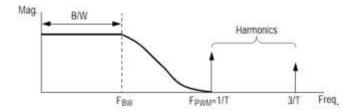

Band width of the desired signal should be  $F_{BW} \leq [F_{PWM}]$ . If  $F_{BW}$  is selected such that,  $F_{BW} = F_{PWM}$  then the external low pass filter should be a brick wall type filter. Brick-wall type analog filter are very difficult and expensive to build. So, for practical purpose, the external low pass filter, that has much smaller cut-off bandwidth than PWM bandwidth, should be used as shown in figure below[6].

348

Figure 2: Bandwidth of Low Pass filter.

The 2nd order low-pass filter offers 40 dB/decade of stop band roll off, which is a two-fold improvement over the 1st order filter. The transfer function is given by the equation.

$$\frac{V_{out}(s)}{V_{In}(s)} = \frac{\omega_n^2}{s^2 + 2\varsigma \boldsymbol{\omega}_n + \omega^2}$$

Where  $\omega n$  is the undammed natural frequency in units of (rad/s) 2 and  $\zeta$  is the non-dimensional damping ratio. It is straightforward to show that the filter bandwidth is BW [7].

BW =

$$\omega_n \left[ (1 - 2\varsigma^2) + \sqrt{4\varsigma^4 - 4\varsigma^2} + 2 \right]^{1/2}$$

## MODELING AND SIMULATION

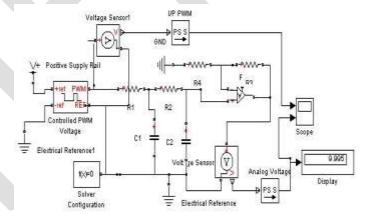

Figure 3: Simulation of DAC.

## **RESULTS:-**

| Sr. | % Duty Cycle | Analog Voltage |

|-----|--------------|----------------|

| no  |              | V              |

| 1   | 10           | 1.023          |

| 2   | 20           | 2.046          |

| 3   | 30           | 3.068          |

| 4   | 40           | 4.091          |

| 5   | 50           | 5.113          |

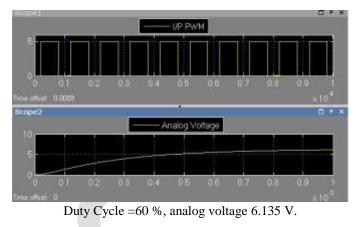

| 6   | 60           | 6.135          |

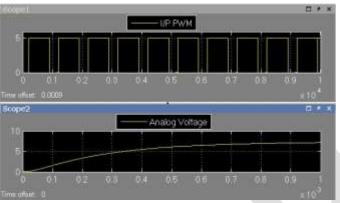

| 7   | 70           | 7.157          |

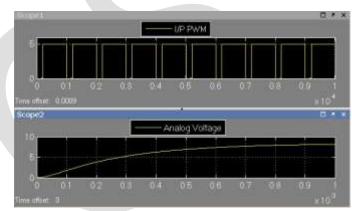

| 8   | 80           | 8.178          |

| 9   | 90           | 9.919          |

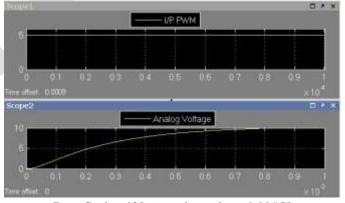

| 10  | 100          | 9.995          |

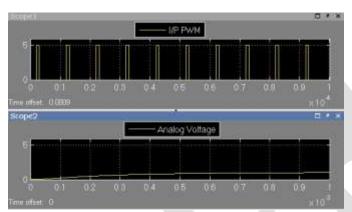

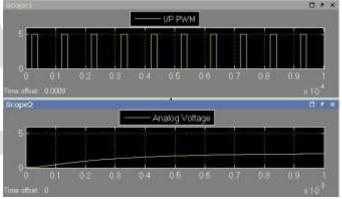

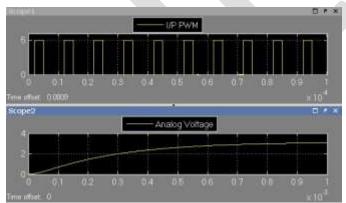

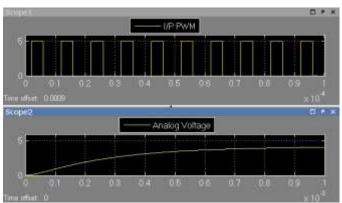

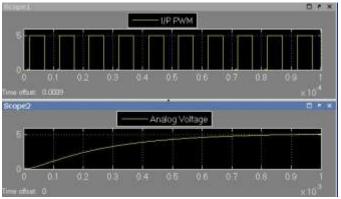

Wave forms for each % Duty Cycle

Duty Cycle =10 %, analog voltage 1.023 V.

Duty Cycle =20 %, analog voltage 2.046 V.

Duty Cycle =30 %, analog voltage 3.068 V.

Duty Cycle =40 %, analog voltage 4.091 V

350

Duty Cycle =50 %, analog voltage 5.113 V.

Duty Cycle = 70 %, analog voltage 7.157 V.

Duty Cycle =80 %, analog voltage 8.178 V.

Duty Cycle =90 %, analog voltage 9.119 V.

Duty Cycle =100 %, analog voltage 9.995 V.

### **MATERIALS**

The simulation model is developed under Matlab 7.0 With Dell XPS m1210 machine core 2 duo processor and 1 GB Ram on windows 7 platforms. Actual circuit is built with PIC18f4550 microcontroller having high speed PWM facility. Optoisolator PC817 is used for PLC and Module isolation. Ladder program written for Mitsubishi FX-2N PLC used with Gx Developer.

Figure 4: Ladder to generate frequency signal.

351

#### **REFERENCES:**

- [1] Cannillo, F.; Imec, Leuven, Belgium; Prefasi, E.; Hernandez, L.; Pun, E. "1.4V 13μW 83dB DR CT-ΣΔ modulator with Dual-Slope quantizer and PWM DAC for biopotential signal acquisition" ESSCIRC (ESSCIRC), 2011ESSCIRC (ESSCIRC), 2011 12-16 Sept. 2011.PP 267 270.

- [2] Della Colletta, G.; Grupo de Microeletronica, Univ. Fed. de Eng. de Itajuba-UNIFEI, Itajuba, Brazil; Ferreira, L.H.C.; Pimenta, T.C. "A low power Successive Approximation A/D converter based on PWM technique" Circuits and Systems (LASCAS), 2012 IEEE Third Latin American Symposium on Feb. 29 2012-March 2 2012. PP 1 4.

- [3] Wright, P.S.; Nat. Phys. Lab., Teddington, UK; Pickering, J.R. "An AC voltage standard based on a PWM DAC" Instrumentation and Measurement, IEEE Transactions on (Volume:48, Issue: 2) PP 457 461.

- [4] Chun Wei Lin; Department of Electronic Engineering, National Yunlin University of Science & Technology, 64002, Taiwan; Sheng Feng Lin "A BIST scheme for testing DAC" Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), 2012 9th International Conference on 16-18 May 2012, pages 1-4.

- [5] Wang Yan-wei; Inst. of Wood Ind., Chinese Acad. of Forestry, Beijing, China; Cheng Fang; Zhou Yu-cheng; Xu Jia-he "Analysis of double-T filter used for PWM circuit to D/A converter" Control and Decision Conference (CCDC), 2012 on 23-25 May 2012 pages 2752 2756.

- [6] Andy Britton "Digital Filters for Analogue Engineers" June 2010.

- [7] Digital to Analog Converter by Douglas A. Mercer ('77) Fellow Analog Devices Inc. Wilmington, MA USA (doug.mercer@analog.com)RPI IEEE Student Chapter October22, 2008.

- [8] D/A Conversion Using PWM and R-2R Ladders to Generate Sine and DTMF Waveforms Authors: Rob Stein and John Day Microchip Technology Inc.

- [9] Using PWM Output as a Digital-to-Analog Converter on a TMS320C240 DSP application note.

- [10] AVR131: Using the AVR's High-speed PWM avr application note.

- [11] Chwan-Hwa Wu, Senior Member, IEEE, J. David Irwin, Fellow, IEEE, and Fa Foster Dai, Senior Member, IEEE "Enabling Multimedia Applications for Factory Automation" IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 48, NO. 5, OCTOBER 2001.

- [12] Songchar Jiang "Wireless Communications and a Priority Access Protocol for Multiple Mobile Terminals in Factory Automation" IEEE TRANSACTIONS ON ROBOTICS AND AUTOMATION, VOL. 14, NO. 1, FEBRUARY 1998.

- [13] Adnan Salihbegovic, Vlatko Marinković, Zoran Cico, Elvedin Karavdić b, Nina Delic ETF Sarajevo, Bosnia and Herzegovina b Bosna-S Oil Services Company, Bosnia and Herzegovina "Web based multilayered distributed SCADA/HMI system in refinery application" Computer Standards & Interfaces 31 (2009) 599–612.