# **Derating Analysis for Reliability of Components**

K.Bindu Madhavi<sup>1</sup>, BH.Sowmya<sup>2</sup>, B. Sandeep<sup>2</sup>, M.Lavanya<sup>2</sup>

<sup>1</sup>Associate Professor, Department of ECE, HITAM, Hyderabad

<sup>2</sup>Research Scholar, Department of ECE, HITAM, Hyderabad

**ABSTRACT:** Ensuring reliable operation over an extended period of time is one of the biggest challenge facing present day electronic systems. The increased vulnerability of the components to various electrical, thermal, mechanical, chemical and electromagnetic stresses poses a big threat in attaing the reliability required for various mission critical applications. Derating can be defined as the practice of limiting electrical, thermal and mechanical stresses on devices to levels below their specified or proven capabilities in order to enhance reliability. If a system is expected to be reliable, one of the major contributing factors must be a conservative design approach incorporating part derating. Realizing a need for derating of electronic and electromechanical parts, many manufacturers have established internal guidelines for derating practices.

In this project, a notch filter circuit is used in an aerospace application is selected. Circuit simulation will be carried out by using E-CAD Tools. Further Derating analysis will be done as in the methodology given in MIL-STD-975A and provide design margin against this standard as well.

Key for success of any product lies in its producibility, Quality and reliability. A lot of effort is needed to develop a new product, make a prototype and prove its performance. Still more effort is required, if it is to be produced in large quantities with minimum number of rejections. Minimum number of rejections or increase in First time yield saves production costs, testing time and resources. Hence it helps to reduce cost of item. It is also required that product delivered to the customer should perform satisfactorily without failure under its expected life cycle operational stresses. It should continue this performance over its expected operational life time, or whenever it is required to operate, a factor which is called reliability. Reliable product performance increases customer satisfaction and gives Brand name for manufacturer.

The increased vulnerability of the components to various electrical, thermal, mechanical, chemical and electromagnetic stresses poses a big threat in attaing the reliability required for various mission critical applications. Derating is the practice of operating at a lower stress condition than a part's rating.

## INTRODUCTION:

Derating is the reduction of electrical, thermal, and mechanical stresses applied to a part in order to decrease the degradation rate and prolong the expected life of the part. Derating increases the margin of safety between the operating stress level and the actual failure level for the part, providing added protection from system anomalies unforeseen by the designer.

## **DERATING CRITERIA**

The derating criteria contained herein indicate the maximum recommended stress values and do not preclude further derating. When derating, the designer must first take into account the specified environmental and operating condition rating factors, consider the actual environmental and operating conditions of the applications, and then apply the recommended derating criteria herein. Parts not appearing in these guidelines are lacking in empirical data and failure history, The derating instructions are listed for each commodity in the following paragraphs.

To assure that these derating criteria are observed, an EEE parts list (item by item) shall be generated for each hardware assembly. This list shall, as a minimum, contain the maximum rated capability (such as voltage, current, power, temperature, etc.) of the part in comparison with the design requirements of the application, indicating conformance to the derating criteria specified herein.

In the following derating sections, the term "ambient temperature" as applied to low pressure or space vacuum operation, is defined as follows:

For operation under conditions of very low atmospheric pressure or space vacuum, heat loss by convention is essentially zero, so ambient temperature is the maximum temperature of the heat sink or other mounting surface in contact with the part, or the temperature of the surface of the part itself (case temperature).

## DERATING LEVELS

The range of derating is generally defined as a point between the minimum derating point and the point of over-derating. The optimum derating, therefore, should occur at or below the point of stress (i.e., voltage, temperature) where a rapid increase in failure rate occurs for a small increase in stress.

#### PART QUALITY LEVELS

Derating cannot be used to compensate for using parts of a lower quality than necessary to meet usage reliability requirements. The quality level of a part has a direct effect on the predicted failure rate.

These derating criteria for hybrid devices such as Integrated circuits, Transistors, Capacitors, Resistors these devices may use thick film or thin films as interconnections and resistive elements. The primary failure modes are failures of active components, integrated circuits or transistor chips, and interconnection faults.

The derating criteria for other complex integrated circuits such as LSI, VHSIC, VLSI, Microprocessors), for the memory devices such as Bipolar, MOS, which are broken up into RAM (Random access memories) and ROM (Read only memories), for Microwave devices such as GaAs FET, Detectors and Mixers, Varactor diodes, Step recovery diodes, PIN diodes, Tunnel diodes, IMPATT diodes, Gunn diodes, and Transistors. The derating criteria procedure is even carried out for Surface Acoustic Wave (SAW) devices such as Delay lines, Oscillators, Resonators, and Filters.

In this project we are derating the hybrid devices which are Resistors, Capacitors and Operational Amplifiers by using an E-CAD Tool MULTISIM which is a circuit simulator developed by SPICE and designed as per the MIL.STD 975M.

## RESISTORS DERATING CRITERIA

The derated power level of a resistor is obtained by multiplying the resistor's nominal power rating by the appropriate power ratio found on the (y) axis in the graphs below and on the next page. This ratio is also a function of the resistor's ambient temperature maximum (x axis). The voltage applied to resistors must also be controlled. The maximum applied voltage should not exceed 80% of the specification maximum voltage rating of PR which ever is less, where:

P = Derated Power (watts).

R = Resistance of that portion of the element actually active in the circuit.

This voltage derating applies to DC and Regular waveform AC applications.

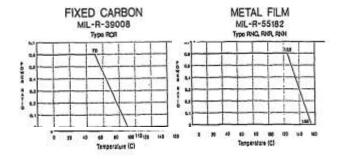

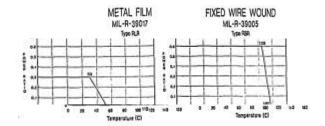

Fig: Resistor derating chart

Power and ambient temperature are the principal stress parameters. Thus by following these parameters based as per MIL.STD 975M and datasheet rules the resistors have been derated which are present in the design.

There are many military specifications that deal with different types of resistors; listing of Resistor MIL Specs.

## CAPACITOR DERATING CRITERIA

Voltage derating is accomplished by multiplying the maximum operating voltage by the appropriate derating factor. The principal stress parameters for capacitors are temperature and DC and/or AC voltage.

## **OP - AMPS DERATING CRITERIA**

The principal stress parameters for linear microcircuits are the supply voltage, input voltage, output current, total device power, and junction temperature.

Even though a component is rated to a particular maximum temperature, derating will insure a worst-case design. So that some unpredictable event, operating condition or design uncertainty does not cause a component to over-heat. However even without derating an integrated circuit is normally specified below its maximum temp, because of part-to-part variations.

So there is always some head room, but the concern is about reliability and good design practices. Derating is a sound design practice because it lowers the junction temperature of the device increasing component life, and reliability.

First stage where factors of producibility, reliability can be taken care is Design phase. Things can be improved later but only with higher costs. One important step that needs to be done during Design stage is simulation with E-CAD tool i.e MULTISIM. Multisim is a circuit simulator powered by SPICE which is the industry standard circuit simulation engine, developed here at Berkeley.

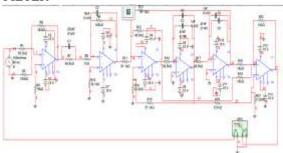

Fig: Outlook of the simulation tool

Many Designers perform simulation and basic nominal functional performance analysis of an Electronic circuit during Design stage. This involves application of appropriate inputs to circuit, simulation and examination of outputs for expected/designed behavior. All component parameters are set to their nominal values. This approach proves circuit behavior at nominal component values. A NOTCH FILTER circuit used in an aerospace application is taken up for analysis. The schematic that has been simulated for the analysis procedure is the notch filter. Notch filter is a band- stop filter with a narrow stop band (or) band - rejection filter of high Q- factor. The performance parameter for the schematic is notch frequency value. Tolerance for this performance parameter is specified. For carrying out this derating analysis procedure we estimate the minimum and maximum currents , voltages , temperature and the required parameters that are considered for any component specifications some of those components are resistors , capacitors, operational amplifiers etc. First simulation is run at nominal values for all component values in schematic. Finally optimum component tolerances, which give low rejection rate during production, are obtained.

#### DESIGN ANALYSIS OF THE NOTCH FILTER

Fig: Notch filter schematic design

In above schematic, FD and FB are analog inputs with a dynamic range of  $\pm$  10 Volts. OUT is analog output with a dynamic range of  $\pm$  10 Volts.V1 and V2 are Voltage sources used to simulate the circuit. Above circuit exhibits notch Frequency at 90 Hz with respect to input on FD with FB grounded.

#### **NOMINAL FUNCTIONAL ANALYSIS:**

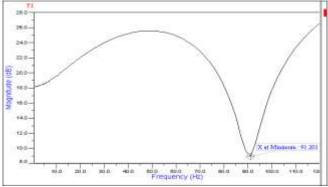

A nominal functional simulation is run by using an EDA tool, with all component values set to nominal.V2 voltage source is set to 0 V to ground FB input.V1voltage source is set to 0.1 V rms sine wave to perform Frequency response Analysis with respect to FD input.Expected nominal value of Notch Frequency is 90±3 Hz.Frequency Response on OUT for nominal simulation is shown below in Fig.It is giving a value of 91.20 Hz as Notch Frequency value, which is as per expectation.

Fig: Nominal Functional Analysis of Notch Frequency

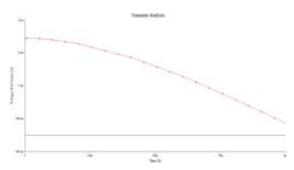

The simulation process consists of AC ANALYSIS, TRANSIENT ANALYSIS and even DC ANALYSIS. The simulation is being carried out with and without presence of load and at different temperatures for checking of design margin and longetivity of the components.

## **Conclusion:**

The outputs that are observed are shown below:

AC ANALYSIS:

Frequency response is observed from magnitude and phase plots .

Many more steps are required to make a reliable product. Product should have a reliability program as per US Military standard.

## **REFERENCES:**

- [1]Dillard, R.B., Reliability for the Engineer, Book Two, Martin Marietta Corporation, 1973.

- [2]"Electronic Reliability Design Handbook," MIL-HDBK-338-1A, October 1988.

- [3]Klion, Jerome, A Redundancy Notebook, Rome Air Development Center, RADC-TR-77-287, December 1987.

- [4]Lalli, Vincent R. and Speck, Carlton E., "Traveling-Wave Tube Reliability Estimates, Life Tests, and Space Flight Experience," NASA TM X-73541, January 1977.

- [5]"Reliability Modeling and Prediction," MIL-STD-756B, November 1981.

- [6] Reliability of components, MIL-STD-975M.

- [7]National Instruments tutorials and general information:

- [8] Transitioning from PSPICE to NI Multisim: A Tutorial http://zone.ni.com/devzone/cda/tut/p/id/5964

- [9] Adding components to your database: http://zone.ni.com/devzone/cda/tut/p/id/5607#toc1

- [10[Ultiboard PCB layout system: http://digital.ni.com/manuals.nsf/websearch/D97873AF18C4EA84862571F5006D0EF3 http://www.opsalacarte.com/Pages/reliability/reliability\_des\_comp.html